### Süsteemide diagnostika

### 5. Testide analüüs

#### 5.1. Rikete simuleerimise meetodid

#### 5.2. Testide analüüs deduktiivsete meetoditega

#### 5.3. Rikete simuleerimine ja analüüs mäluga skeemides

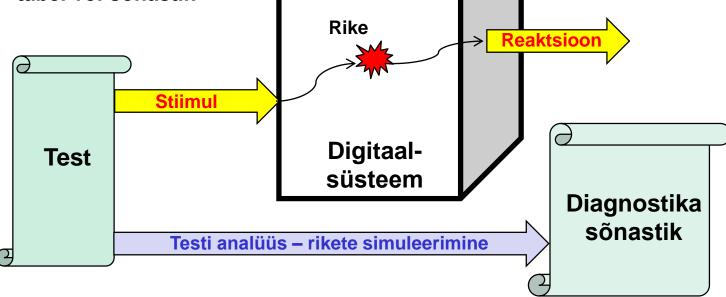

## Testide analüüs

# Rikete simuleerimise eesmärgid:

- Arvutada rikete kate (testi kvaliteet)

- Konstrueerida rikete tabel või sõnastik

## **Faults in Digital Circuits**

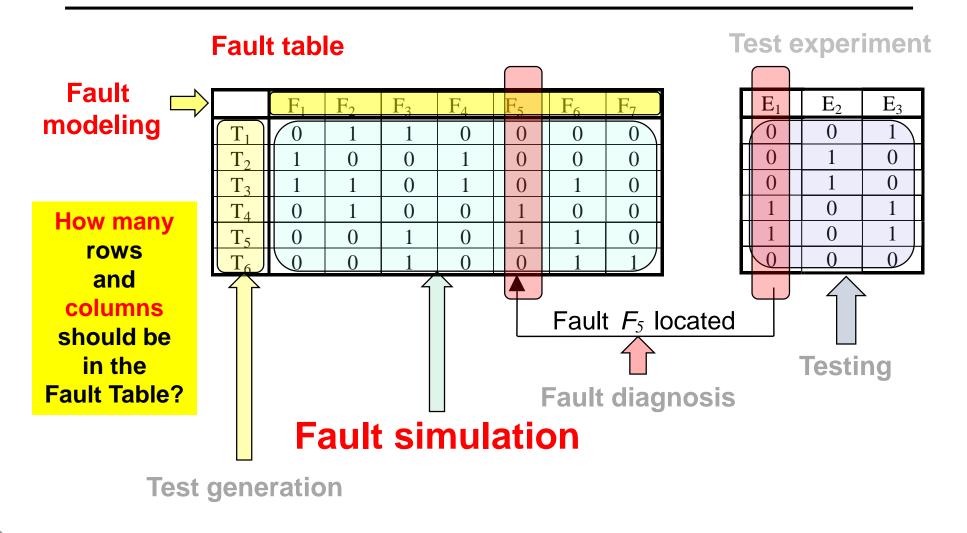

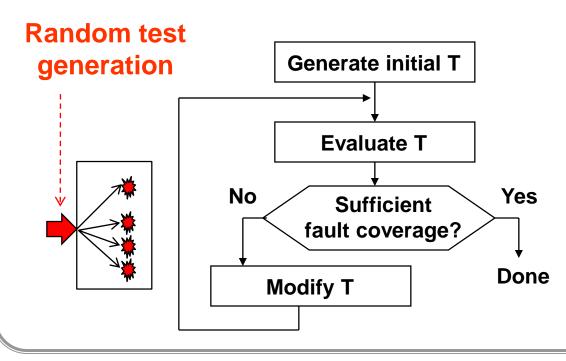

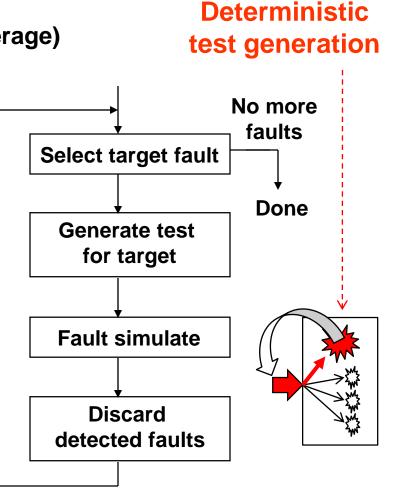

## **Fault simulation**

#### **Goals:**

- Evaluation (grading) of a test T (fault coverage)

- Guiding the test generation process

- Constructing fault tables (dictionaries)

- Fault diagnosis

### Impact of Scan-Path: Fault Simulation

**Fault simulation is needed for:** test generation, fault diagnosis, test quality analysis, design verification, fault tolerance evaluation...

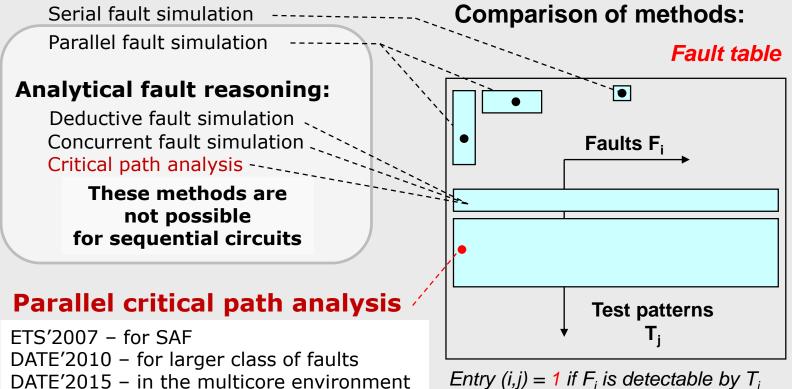

#### Fault simulation techniques:

TALLINN UNIVERSITY OF TECHNOLOGY

Entry (i,j) = 1 if  $F_i$  is detectable by  $T_j$ Entry (i,j) = 0 if  $F_i$  is not detectable by  $T_j$

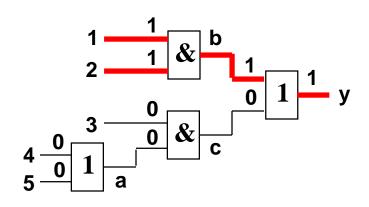

### Single and Parallel SAF Fault Simulation

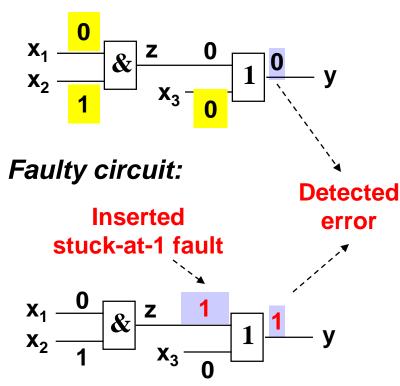

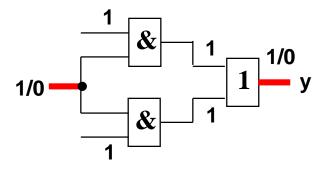

### Single pattern

Fault-free circuit:

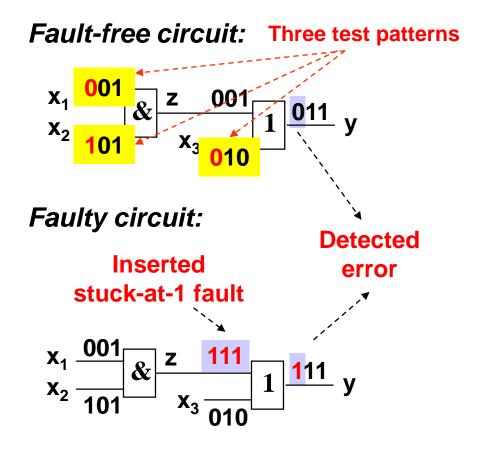

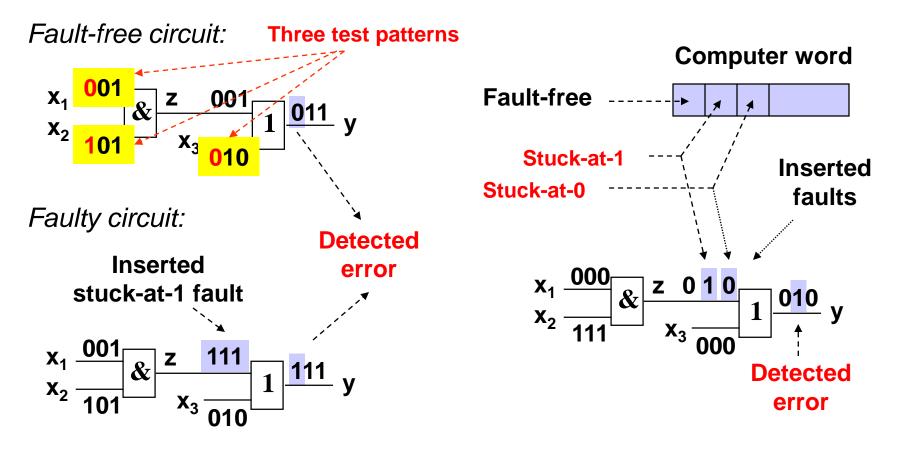

#### **Parallel patterns**

### **Parallel Fault & Test Pattern Simulation**

#### **Parallel patterns**

#### **Parallel faults**

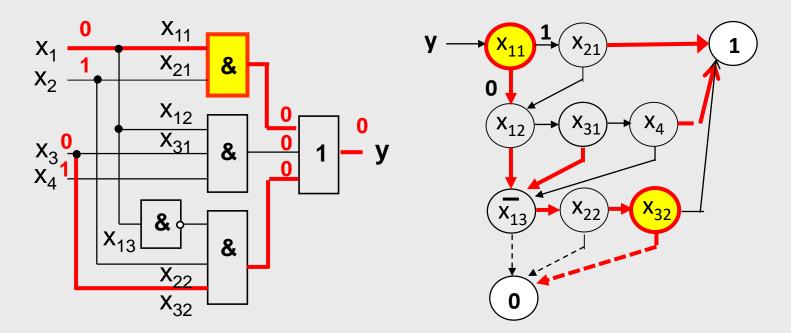

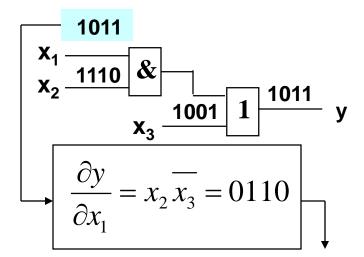

### Fault Analysis with SSBDDs

#### **Algorithm:**

- 1. Determine the activated path to find the fault candidates

- 2. Analyze the detectability of the each candidate fault (each node represents a subset of real faults)

1918 **Tallinna Tehnikaülikool** Tallinn University of Technology

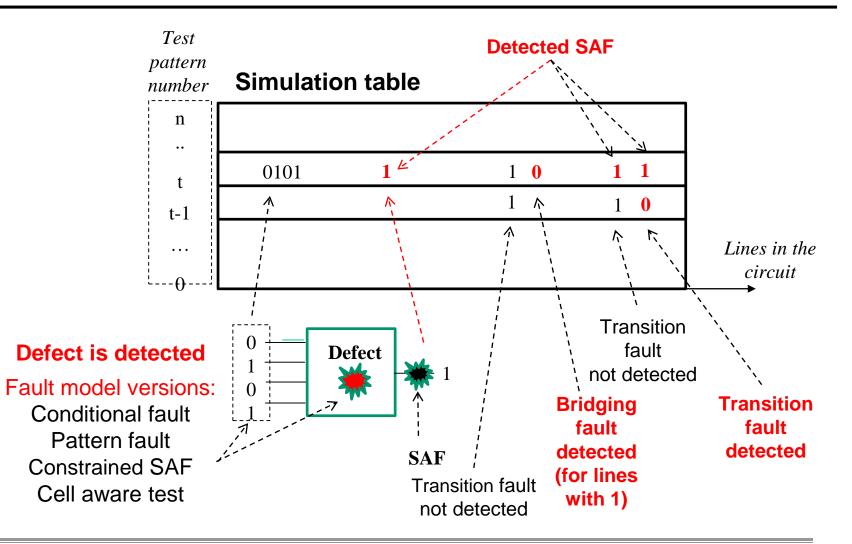

### **Simulation of Diferent Classes of Faults**

### Süsteemide diagnostika

### 5. Testide analüüs

10

5.1. Rikete simuleerimise meetodid

#### 5.2. Testide analüüs deduktiivsete meetoditega

#### 5.3. Rikete simuleerimine ja analüüs mäluga skeemides

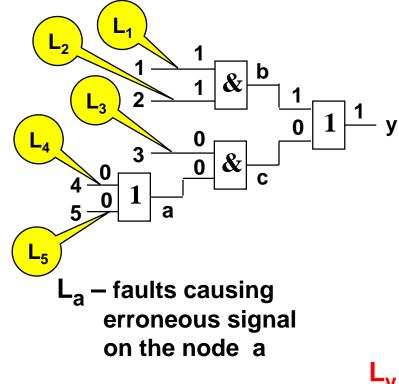

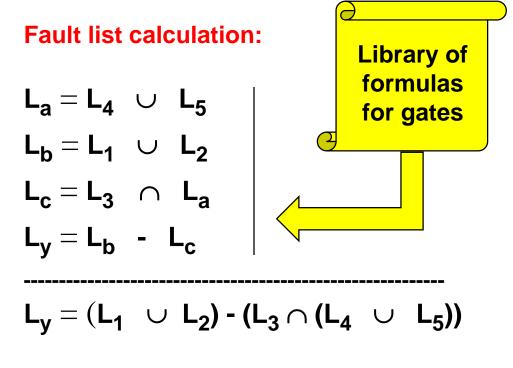

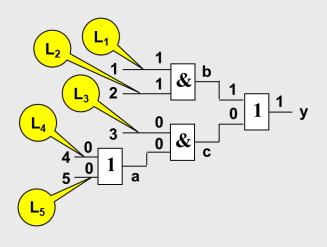

### **Deductive Fault Simulation**

#### **Gate-level fault list propagation**

L<sub>y</sub> – faults causing erroneous signal on the output node y

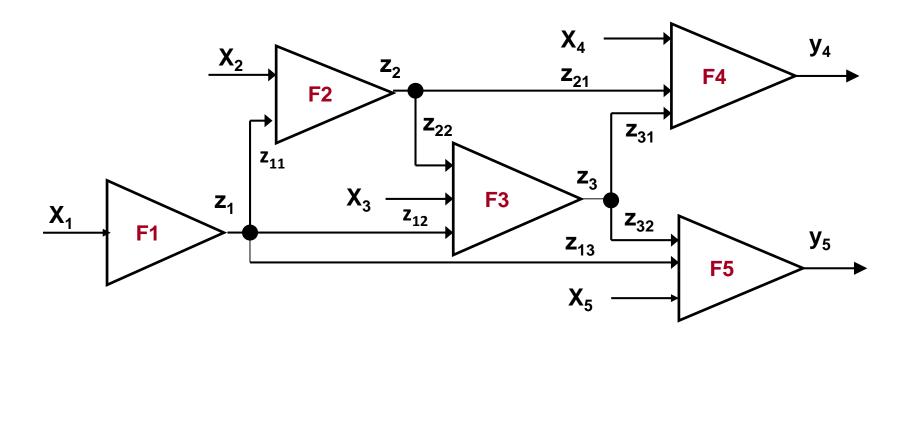

## Fault Analysis with SSBDDs

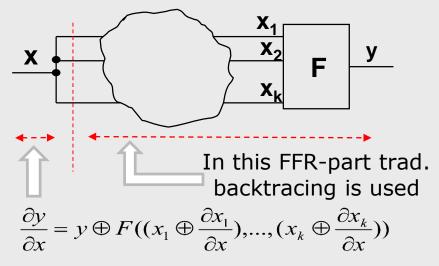

The components to be analyzed may be also fan-out free regions (FFR), and the fault propagation can be calculated with SSBDDs

#### **X**<sub>11</sub> $X_1$ **X**<sub>21</sub> & **X**<sub>2</sub> **X**<sub>12</sub> **x**<sub>12</sub> X31 X 0 $\bar{\mathbf{X}}_{31}$ $X_3^{0}$ & У $X_4$ X<sub>27</sub> & **X**<sub>13</sub> & X<sub>22</sub> X<sub>32</sub>

#### **Algorithm:**

- 1. Determine the activated path to find the fault candidates

- 2. Analyze the detectability of the each candidate fault (each node represents a subset of real faults)

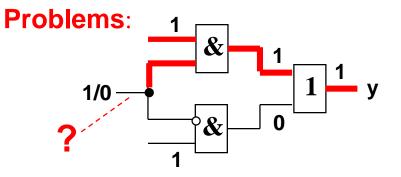

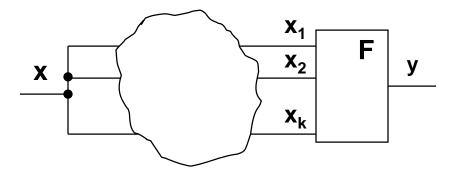

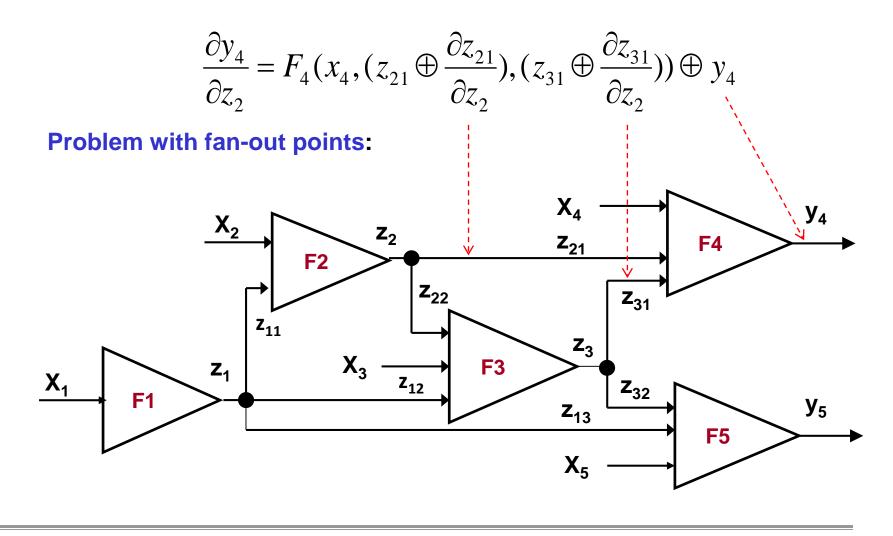

## **Critical Path Tracing**

The critical path breaks on the fan-out

The critical path is not continuous

#### **Problem with fan-out points:**

Detected faults vector: - 10 -

- T1: No faults detected

- T2:  $x_1 \equiv 1$  detected

- T3:  $x_1 \equiv 0$  detected

- T4: No faults detected

Handling of fanout points:

- Fault simulation

- Boolean differential calculus

The critical path is not continuous

The critical path breaks on the fan-out

#### Solution:

Secret of solving the reconvergent fan-out problem:

The result is exact critical path tracing beyond the convergent fan-outs

### Süsteemide diagnostika

### 5. Testide analüüs

18

- 5.1. Rikete simuleerimise meetodid

- 5.2. Testide analüüs deduktiivsete meetoditega

- 5.3. Rikete simuleerimine ja analüüs mäluga skeemides

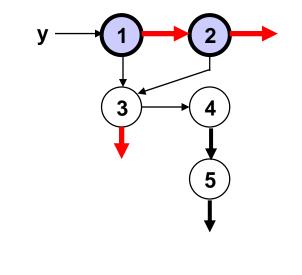

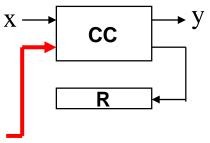

### **Fault Simulation in Sequential Circuits**

Time frame model:

T - 2

T - 1

Current time frame T

У

**Technical University Tallinn, ESTONIA**

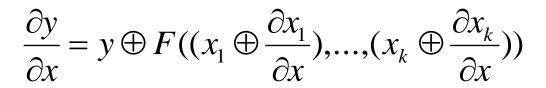

# **DFT-ased Critical Path fault Tracing**

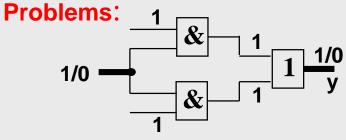

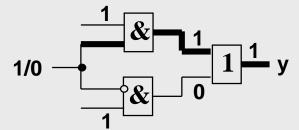

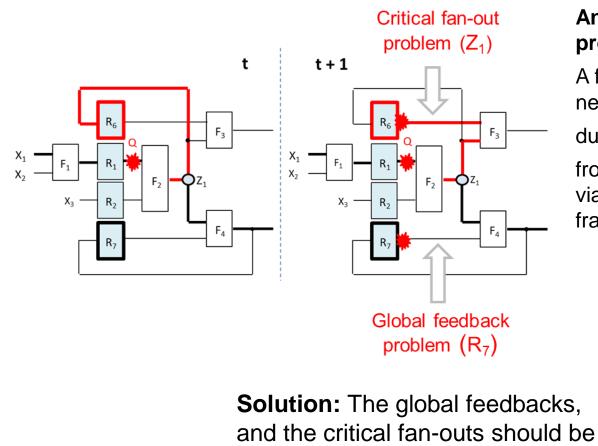

#### Critical path tracing problem:

•Why it is not possible in sequential circuits?

•Because the critical path backtracing is based on reasoning of correct signals in the circuit

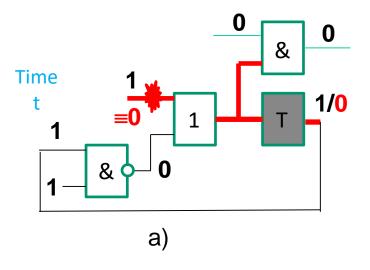

#### Example:

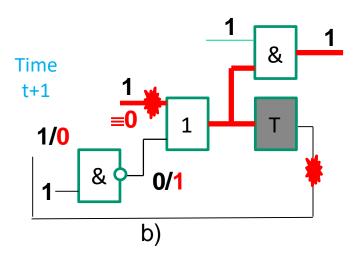

- Two time-frames for simulating two patterns.

- Fault Q propagates from time frame t to t + 1, causing the wrong value in R3

- Hence, backtracing in frame *t* + 1 is not any more possible

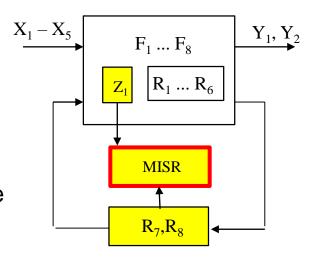

- The sequential circuit has to be modified by cutting a subset of global feedbacks for inserting MISR

- For the remaining part of local feedbacks the critical path tracing method was updated for path tracing over diferent time frames.

# **DFT-based fault simulation**

made observable using MISR

# Another critical path tracing problem:

A fault may corrupt the signals in the next time frame

due to the fan-out,

from which the signals may converge via the paths over diferent time frames

# **DFT-based fault simulation**

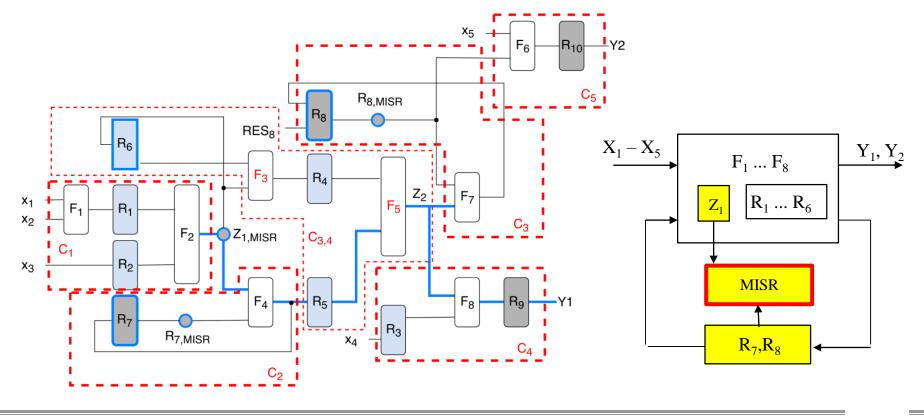

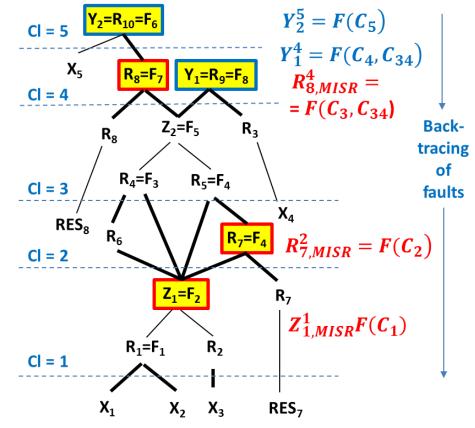

**Example:** A circuit as a Network with two global feedbaks to be cut, and the registers  $R_{7,MISR}$  and  $R_{8,MISR}$  should be made observable.

The fanout  $R_{8,MISR}$  should be made observable as well.

Technical University Tallinn, ESTONIA

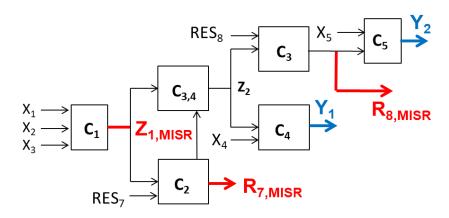

### 2a. DFT-based fault simulation

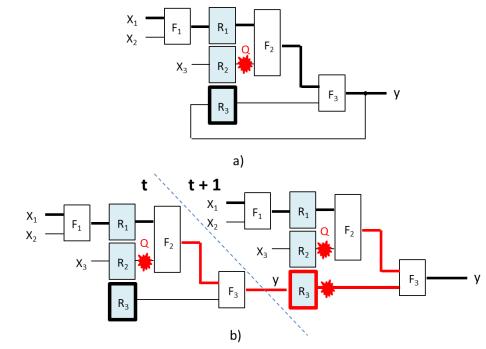

**Solution:** The full circuit is partitioned into the network of combinational subcircuits which can be backtraced (up to the observation points) in diferent time frames

Observation points: outputs Y1 and Y2, and the nodes  $R_{7,MISR}$  ,  $R_{8,MISR}$  ,  $Z_{1,MISR}$  , connected to MISR

**Example:** Critical path fault tracing over 5 time frames similarly as in combinational circuits.

Technical University Tallinn, ESTONIA

# **DFT-based fault simulation**

**Experiments:** We compared the speed-up achieved by the **proposed method** in comparison with single fault simulation method (**FS**) in sequential circuits

| Circuts | Number of | SAF           | Gain in        |                    |          |

|---------|-----------|---------------|----------------|--------------------|----------|

|         | faults F  | Log Sim<br>LS | FaultSim<br>FS | Proposed<br>method | speed, G |

| 8a      | 112034    | 0.155         | 17365          | 30.0               | 579      |

| 8b      | 83940     | 0.152         | 12759          | 24.7               | 517      |

| 8be     | 99330     | 0.168         | 16687          | 62.1               | 269      |

| 8bk     | 86878     | 0.159         | 13814          | 25.2               | 548      |

| 8bs     | 100820    | 0.154         | 15526          | 173.4              | 90       |

| 8c      | 122386    | 0.159         | 19459          | 35.9               | 542      |

| 8d      | 123012    | 0.161         | 19804          | 35.5               | 558      |

| 8de     | 136876    | 0.164         | 22447          | 81.3               | 276      |

The benchmark family (pipelined signal processors) was created in the institut during the Project CEBE (2007-2015) FS = LS \* FGain: G = FS / Proposed method Span: 90 – 579 times

Fault dropping was not used to make the comparison fear with the critical path tracing approach, which produces all detected faults for all patterns simulated The gain depends on the complexity of the circuit in terms of the (nested) reconvergent fan-outs

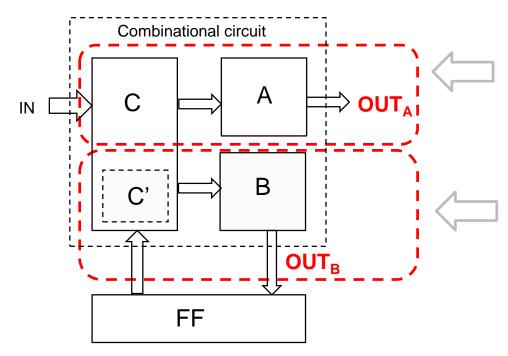

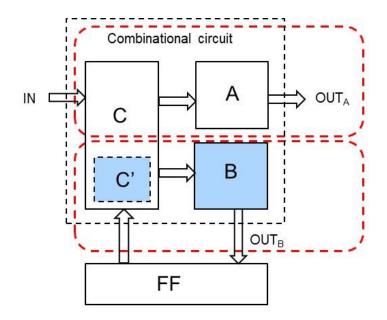

**Exact parallel critical path backtracing** of one group of faults is combined with sequential fault simulation of the remaining group of faults

Combinational part, where fast parallel critical path tracing to  $OUT_A$  is possible

Sequential part, where critical path tracing to  $OUT_A$  in a single clock is not possible

These faults have to be simulated one-by-one in sequence

The faults in C may fall into the both parts Share of the faults, falling into the parts, depends on the test patterns

The fault groups are separated on the simulation flow algorithmically, no DFT modification of the circuit is needed

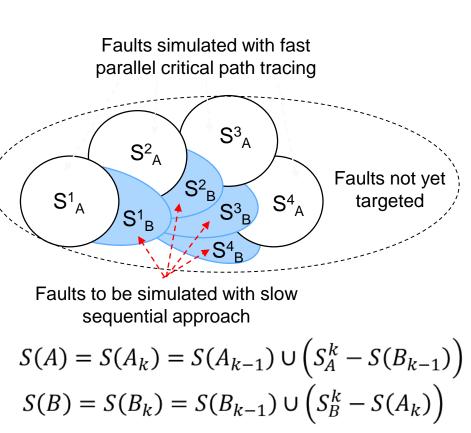

The current state of fault simulation can be expressed after the *k*-th pattern of the test sequence as:

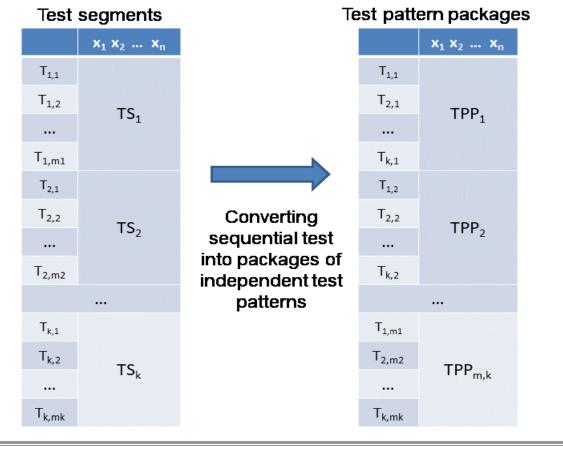

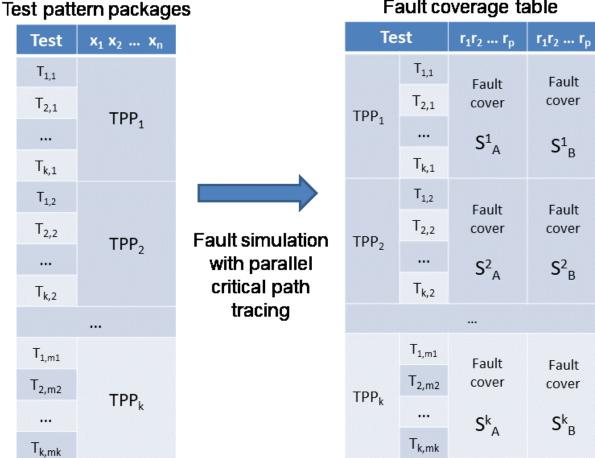

#### Before the fault simulation the set of test sequences is to be converted into the ordered independent pattern packages

Independent test pattern packages can be analyzed by fault backtracing in parallel

#### Solution: Parallel fault backtracking along the critical paths

#### Fault coverage table

**S<sup>1</sup>**<sub>A</sub>: A part of faults in the sequential circuit can be simulated by exact parallel fault backtracing **fast**

**S<sup>1</sup>**<sub>B</sub>: he rest of the faults have to be simulated by **slow** fault-by-fault simulation concept

#### Experimental results: The gain is between 1.9 and 4.2

|    | Circuit | Faults<br># | Fault coverage of               |      | Time for<br>critical path<br>tracing (s) |                 | Total time (s)   |                  |       |     |

|----|---------|-------------|---------------------------------|------|------------------------------------------|-----------------|------------------|------------------|-------|-----|

| #  |         |             | the simulated test sequence (%) |      |                                          |                 | t <sub>NEW</sub> | t <sub>OLD</sub> | Gain  |     |

|    |         |             | s(A)                            | s(B) | FC                                       | t <sub>CP</sub> | t <sub>CL</sub>  |                  |       |     |

| 1  | s526    | 984         | 3.3                             | 32.3 | 35.6                                     | 0.10            | 0.01             | 0.4              | 0.9   | 2.1 |

| 2  | s713    | 1266        | 43.8                            | 37.6 | 81.4                                     | 0.12            | 0.03             | 0.8              | 1.8   | 2.2 |

| 3  | s1494   | 2864        | 37.9                            | 20.2 | 58.1                                     | 0.15            | 0.07             | 1.5              | 6.3   | 4.2 |

| 4  | b05     | 3952        | 2.2                             | 32.2 | 34.4                                     | 0.21            | 0.16             | 4.5              | 13    | 2.9 |

| 5  | s5378   | 9122        | 45.7                            | 26.2 | 71.9                                     | 0.36            | 0.24             | 23               | 85    | 3.7 |

| 6  | s9234   | 16756       | 2.1                             | 30.1 | 32.2                                     | 0.58            | 0.36             | 91               | 300   | 3.3 |

| 7  | s15850  | 29682       | 5.1                             | 32.5 | 37.6                                     | 1.17            | 0.60             | 309              | 946   | 3.1 |

| 8  | b15     | 36496       | 0.6                             | 49.7 | 50.3                                     | 5.35            | 0.65             | 521              | 1036  | 2.0 |

| 9  | s38417  | 69662       | 1.9                             | 50.7 | 52.6                                     | 2.44            | 1.35             | 2516             | 4956  | 1.9 |

| 10 | b17     | 129422      | 0.3                             | 25.0 | 25.3                                     | 15.4            | 1.96             | 3226             | 12857 | 4.0 |

Technical University Tallinn, ESTONIA

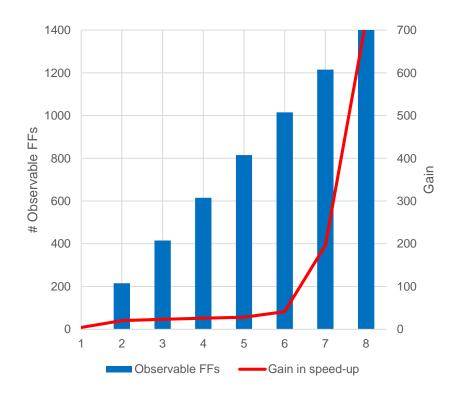

The possible simulation speed-up is defined by the observability of flip-flops

(investigations of the circuit b17)

- ✓ The efficiency of the concept is ecplained by on-line classification of faults into two classes:

- detectable by parallel path tracing,

- to be simulated by traditional methods

- ✓ Speed-up of fault simulation was achieved 1.9 – 4.2 times

- ✓ High scalability was achieved