# **Design for Testability**

### **Outline**

- Ad Hoc Design for Testability Techniques

- Method of test points

- Multiplexing and demultiplexing of test points

- Time sharing of I/O for normal working and testing modes

- Partitioning of registers and large combinational circuits

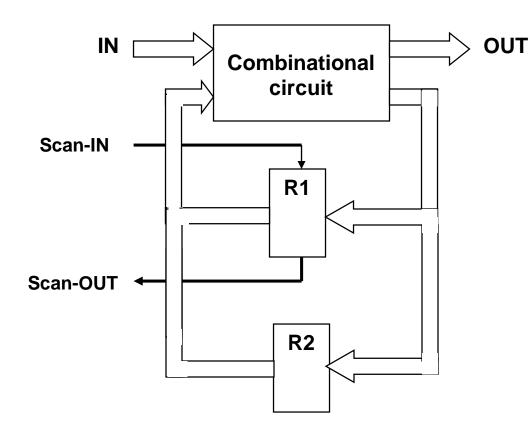

- Scan-Path Design

- Scan-path design concept

- Controllability and observability by means of scan-path

- Full and partial serial scan-paths

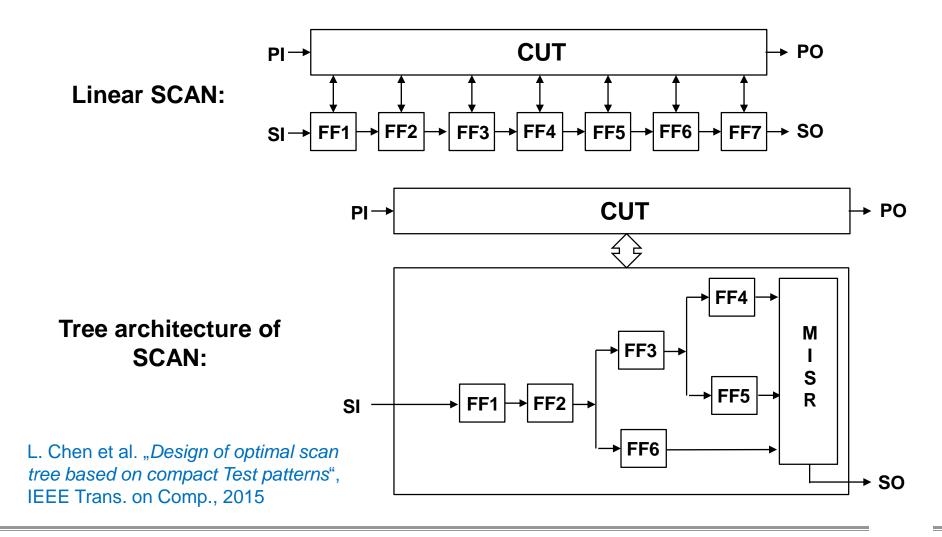

- Non-serial scan design

- Classical scan designs

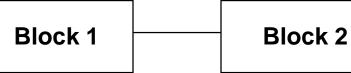

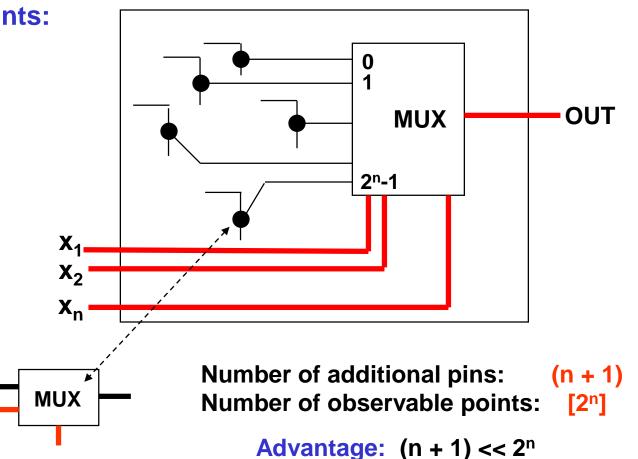

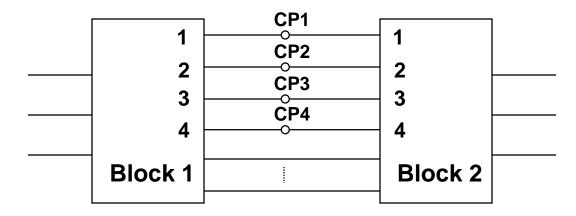

#### **Method of Test Points:**

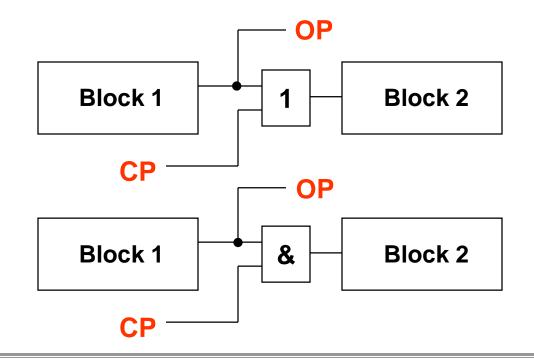

Block 1 is not observable, Block 2 is not controllable

Improving controllability and observability:

#### 1- controllability:

CP = 0 - normal working mode CP = 1 - controlling Block 2 with signal 1

#### **0- controllability:**

CP = 1 - normal working mode CP = 0 - controlling Block 2 with signal 0

#### **Method of Test Points:**

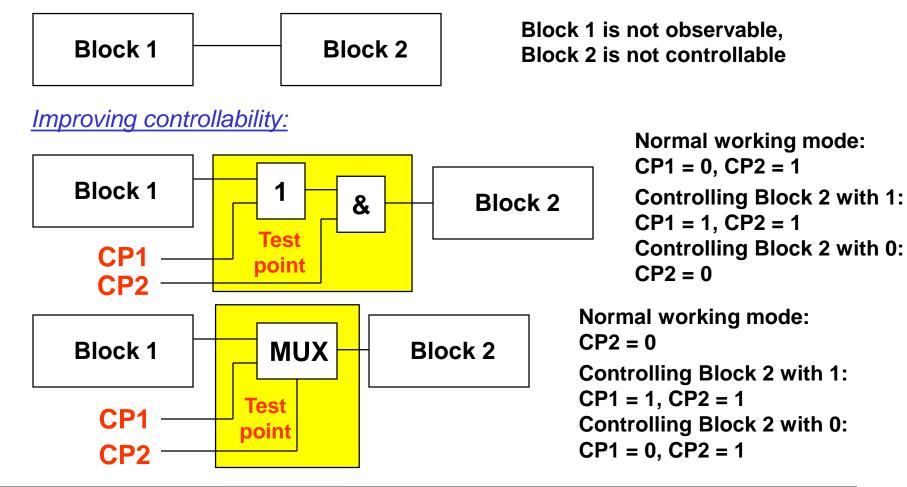

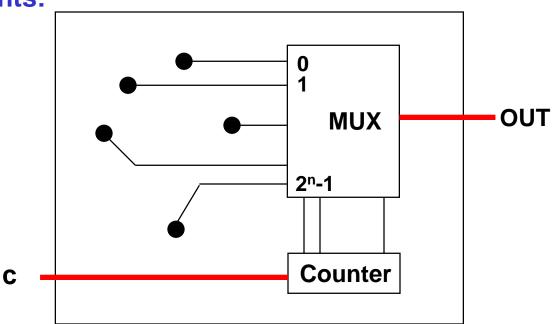

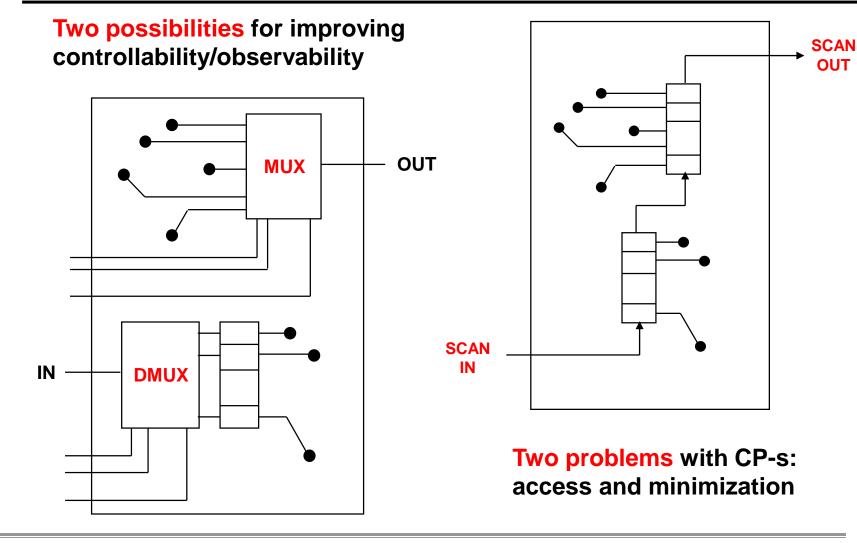

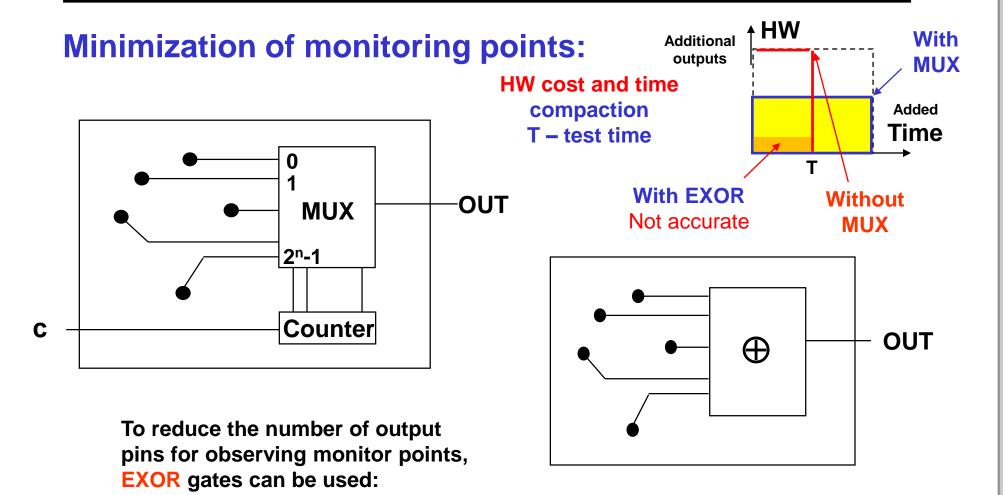

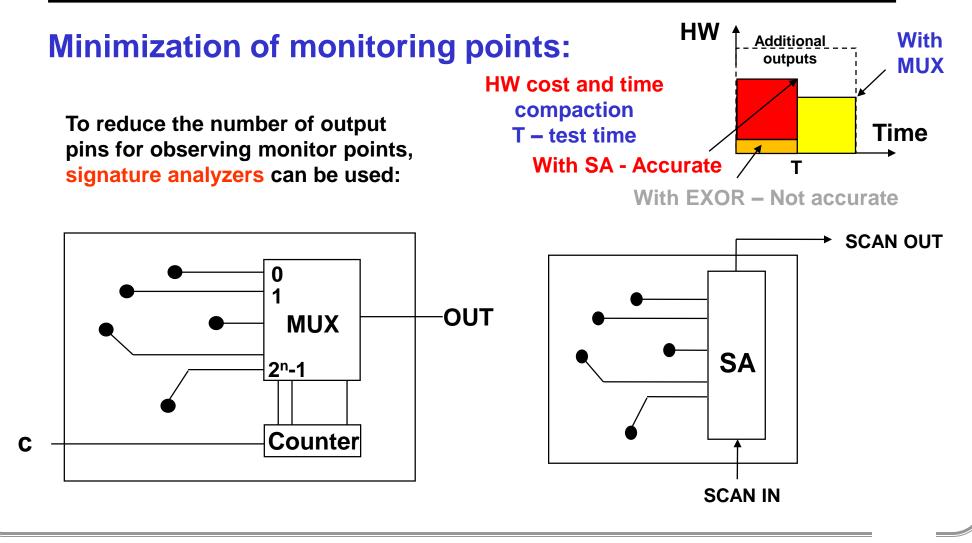

### **Multiplexing monitor points:**

To reduce the number of output pins for observing monitor points, multiplexer can be used:

2<sup>n</sup> observation points are replaced by a single output and n inputs to address a selected observation point

#### **Disadvantage:**

Only one observation point can be observed at a time

### **Multiplexing monitor points:**

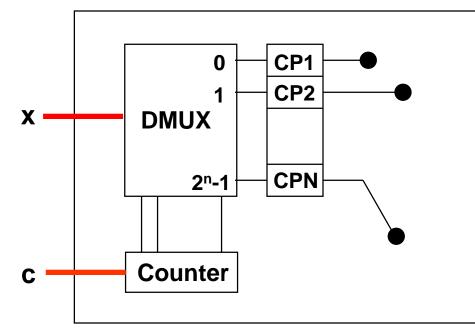

To reduce the number of output pins for observing monitor points, multiplexer can be used:

To reduce the number of inputs, a counter (or a shift register) can be used to drive the address lines of the multiplexer

#### **Disadvantage**:

Only one observation point can be observed at a time

Reset for counter?

Number of additional pins: 2 Nmber of observable points: [2<sup>n</sup>]

```

Advantage: 2 < n << 2<sup>n</sup>

```

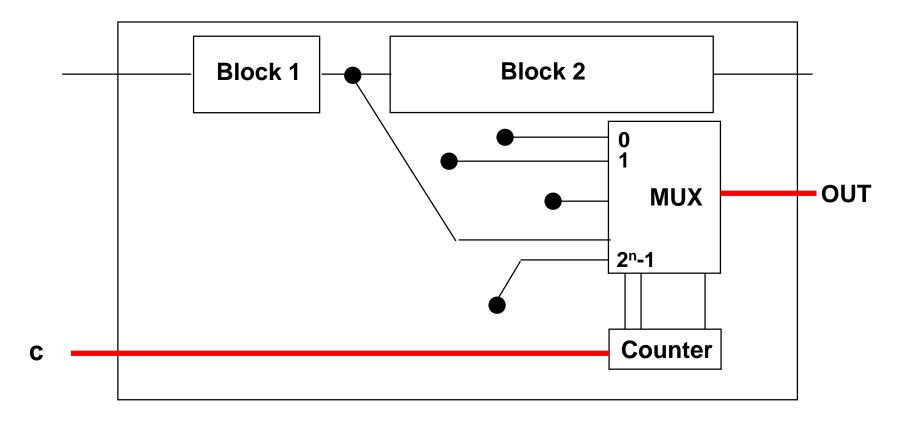

#### **Multiplexing monitor points:**

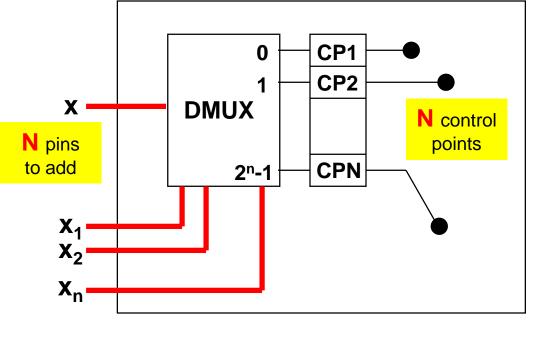

#### **Demultiplexer for implementing control points:**

#### **Demultiplexer for implementing control points:**

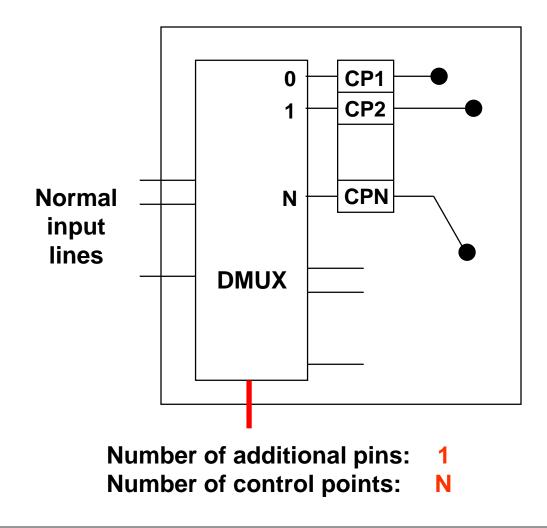

To reduce the number of input pins for controlling testpoints, demultiplexer and latch register are used

Number of additional pins:(n + 1)Number of control points: $2^{n-1} < N \le 2^n$

Advantage: (n + 1) << N

#### **Demultiplexer for implementing control points:**

Number of additional pins:2Number of control points:N

Advantage: 2 << N

To reduce the number of inputs for addressing, a counter (or a shift register) can be used to drive the address lines of the demultiplexer

#### **Disadvantage:**

N clock times are required between test vectors to set up the proper control values

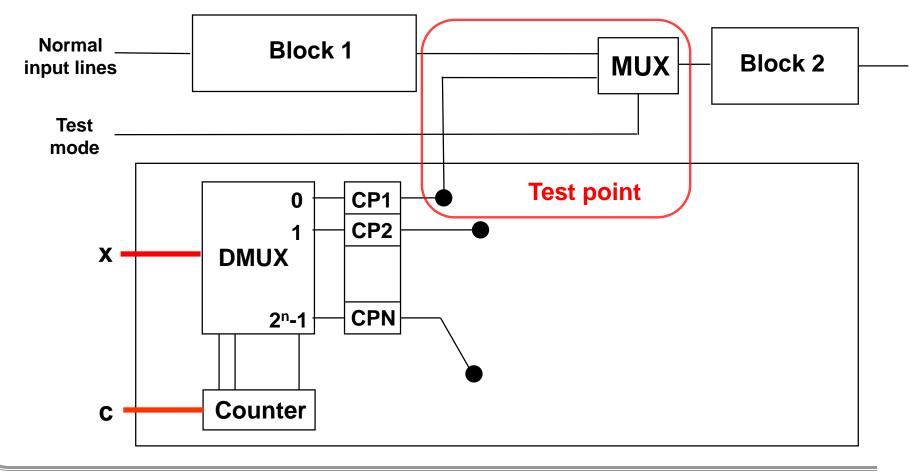

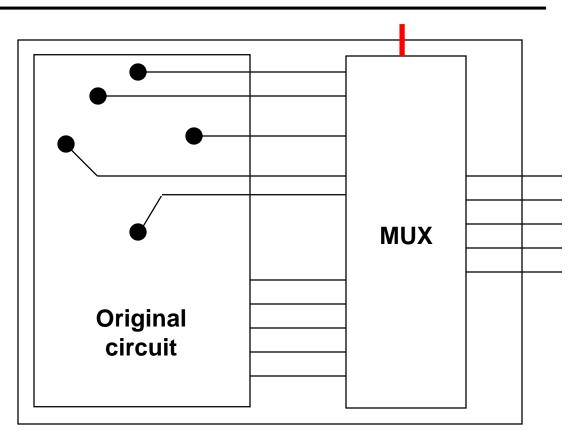

### Time-sharing of outputs for monitoring

To reduce the number of output pins for observing monitor points, timesharing of working outputs can be introduced: no additional outputs are needed

To reduce the number of inputs, again counter or shift register can be used if needed

Number of additional pins: Number of control points: Ν

1

Advantage: 1 << N Test time decreases

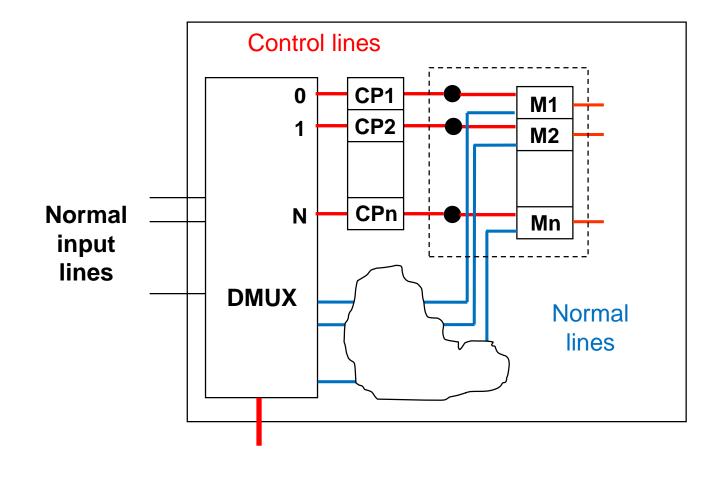

### **Time-sharing of inputs for controlling**

To reduce the number of input pins for controlling test points, time-sharing of working inputs can be introduced.

To reduce the number of inputs for driving the address lines of demultiplexer, counter or shift register can be used if needed

Advantage: 1 < N Test time decreases

## **Time-sharing of inputs for controlling**

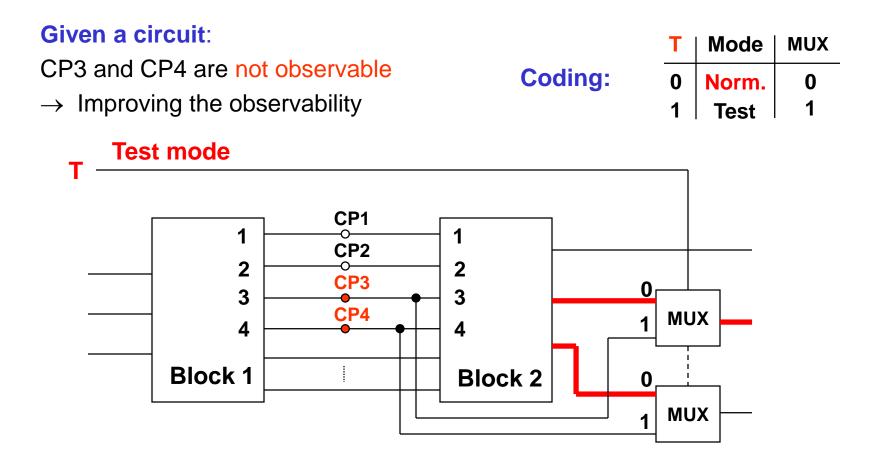

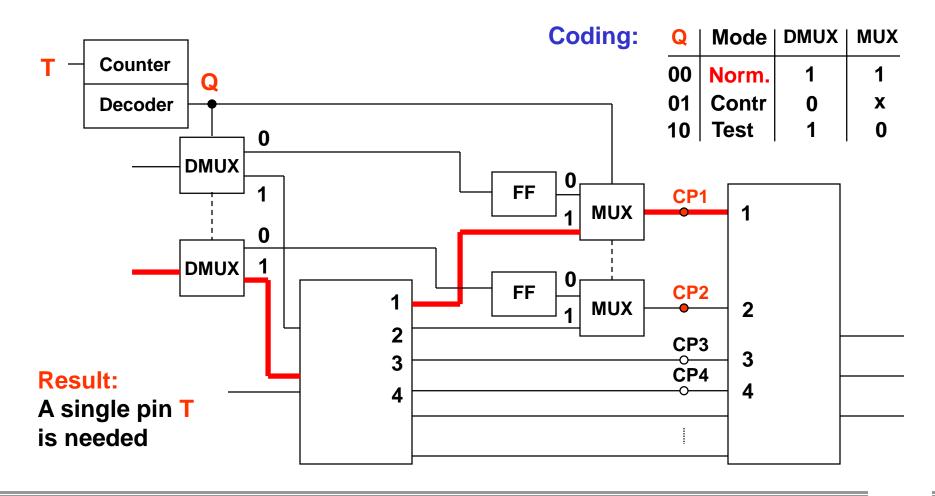

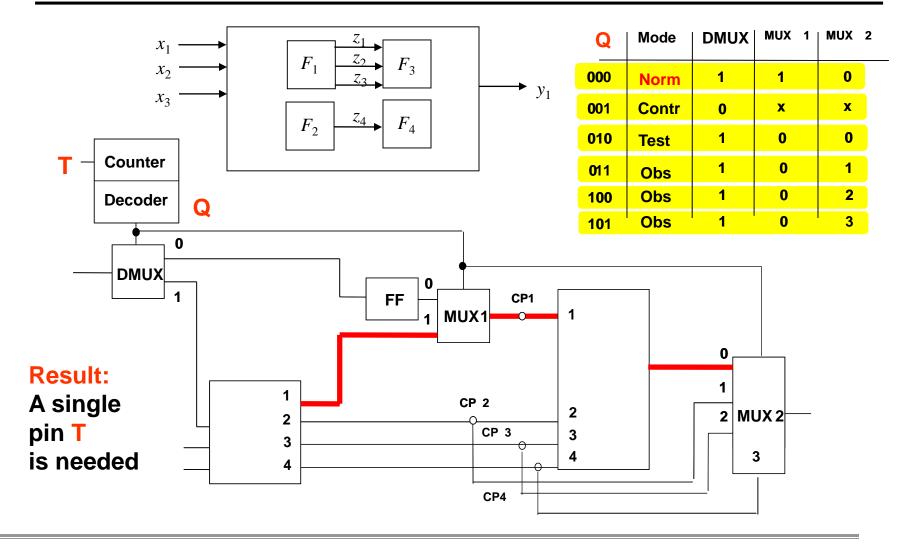

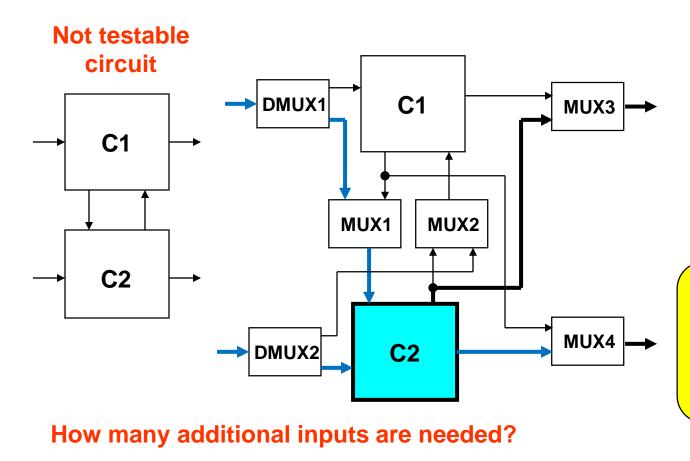

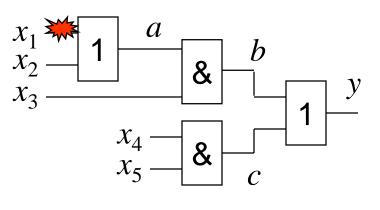

#### Given a circuit:

- CP1 and CP2 are not controllable

- CP3 and CP4 are not observable

**DFT task:** Improve the testability by using a single control input, no additional inputs/outputs allowed

**Result:** A single pin T (test mode) is needed

**Given a circuit**: CP1 and CP2 are not controllable  $\rightarrow$  Improving the controllability

**Technical University Tallinn, ESTONIA**

#### **Examples of good candidates for control points:**

- control, address, and data bus lines on bus-structured designs

- enable/hold inputs of microprocessors

- enable and read/write inputs to memory devices

- clock and preset/clear inputs to memory devices (flip-flops, counters, ...)

- data select inputs to multiplexers and demultiplexers

- control lines on tristate devices

### **Examples of good candidates for observation points:**

- stem lines associated with signals having high fanout

- global feedback paths

- redundant signal lines

- outputs of logic devices having many inputs (multiplexers, parity generators)

- outputs from state devices (flip-flops, counters, shift registers)

- address, control and data busses

### Logical redundancy:

#### Redundancy should be avoided:

- If a redundant fault occurs, it may invalidate some test for nonredundant faults

- Redundant faults cause difficulty in calculating fault coverage

- Much test generation time can be spent in trying to generate a test for a redundant fault

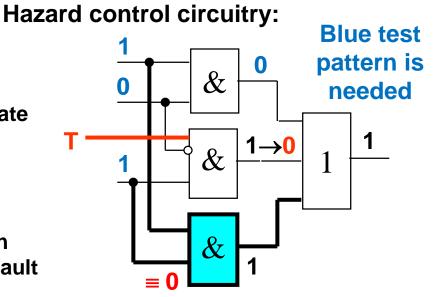

#### **Redundancy intentionally added:**

- To eliminate hazards in combinational circuits

- To achieve high reliability (using error detecting circuits)

Redundant AND-gate Fault  $\equiv 0$  not testable

Additional control input added:

- T = 1 normal working mode

- T = 0 testing mode

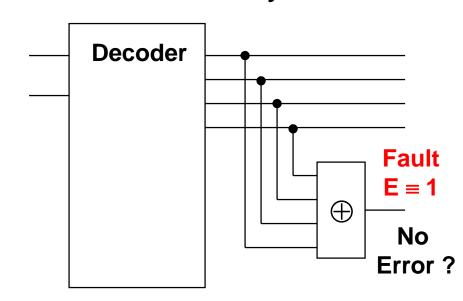

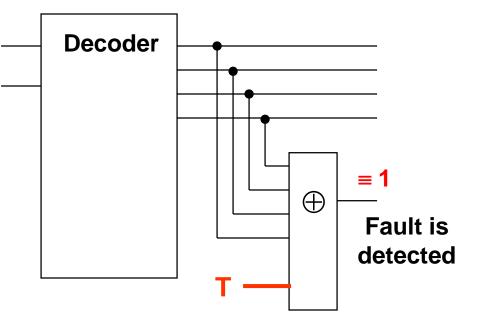

### Fault redundancy:

**Error control circuitry:**

E = 1 if decoder is fault-free Fault = 1 not testable **Testable error control circuitry:**

Additional control input added:  $T \equiv 0$  - normal working mode T = 1 - testing mode

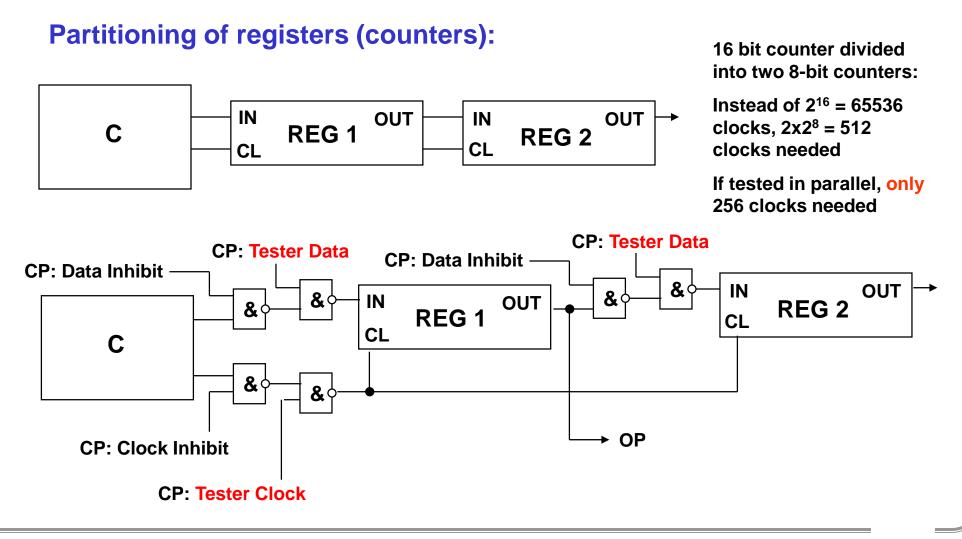

### Partitioning of large combinational circuits:

The time complexity of test generation and fault simulation grows faster than a linear function of circuit size

Partioning of large circuits reduces the test cost

I/O sharing of normal and testing modes is used

# Three modes can be chosen:

- normal mode

- testing C1

- testing C2 (bolded blue lines)

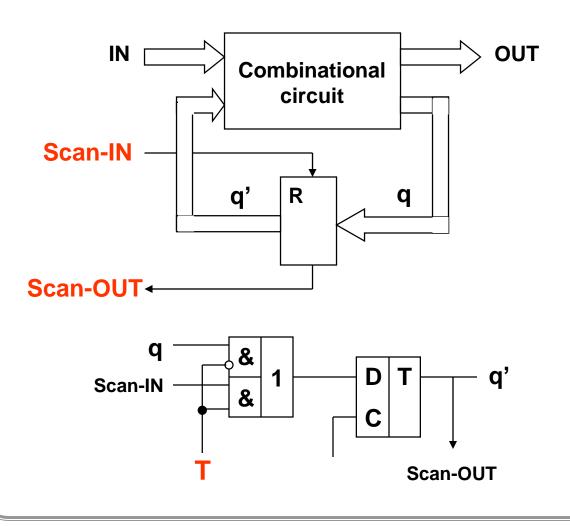

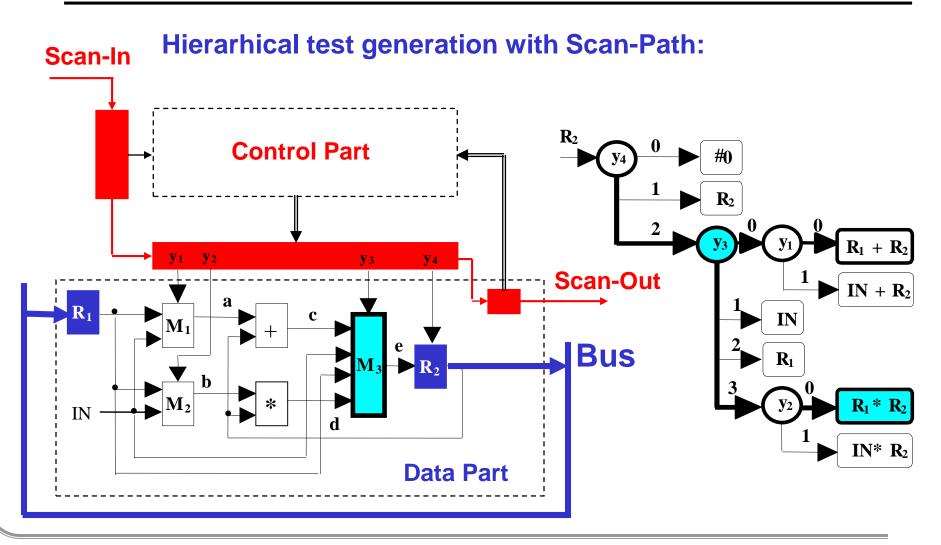

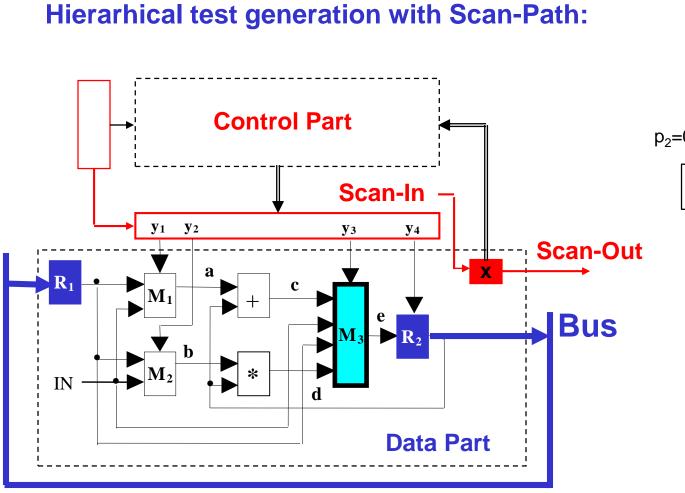

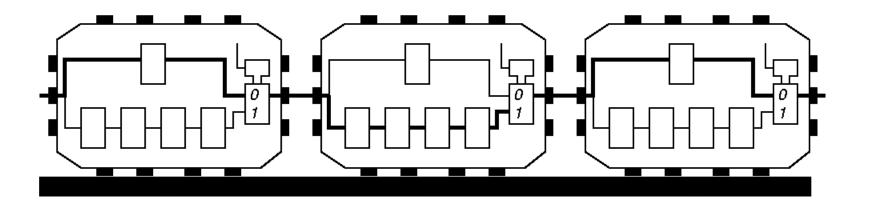

## **Scan-Path Design**

The complexity of testing is a function of the number of feedback loops and their length

The longer a feedback loop, the more clock cycles are needed to initialize and sensitize patterns

Scan-register is a aregister with both shift and parallel-load capability

- T = 0 normal working mode

- T = 1 scan mode

**Normal mode :** flip-flops are connected to the combinational circuit

**Test mode:** flip-flops are disconnected from the combinational circuit and connected to each other to form a shift register

### **Design for Testability & Control Points**

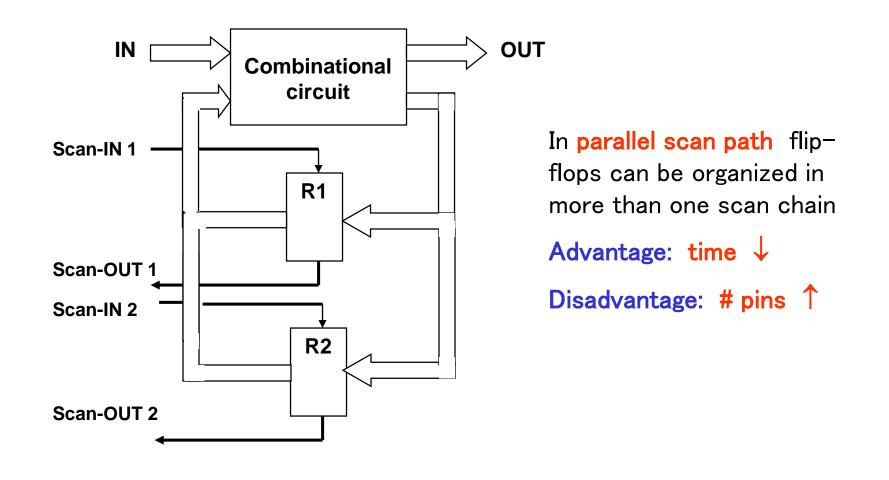

### **Parallel Scan-Path**

### **Partial Scan-Path**

In partial scan instead of full-scan, it may be advantageous to scan only some of the flip-flops

*Example:* counter - even bits joined in the scanregister

### Linear Scan-Path vs Tree Architecture

### **Partial Scan Path**

Technical University Tallinn, ESTONIA

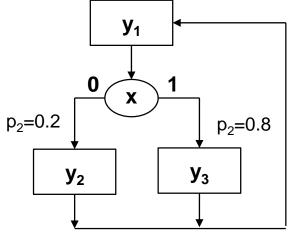

# **Testing with Minimal DFT**

If the control flow sequences are short, only a single or few flip-flops of datadependent flag-FF-s are included into the scan-path

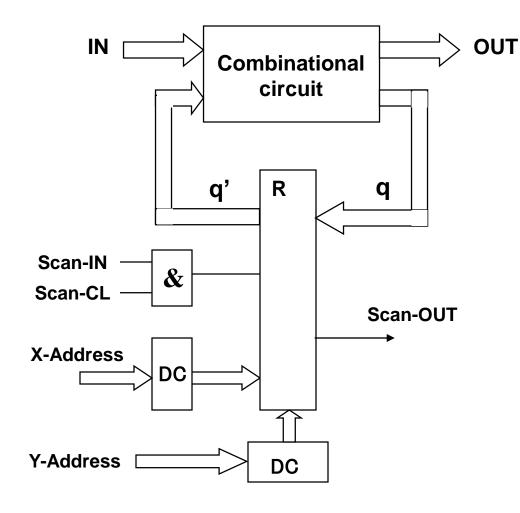

### **Random Access Scan**

In random access scan each flip-flop in a logic network is selected individually by an address for control and observation of its state

#### Example:

Delay fault testing

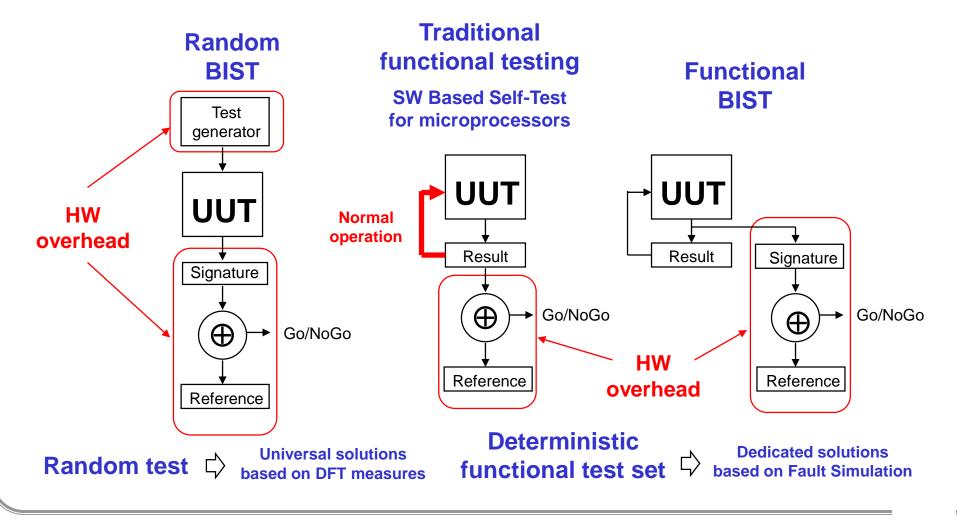

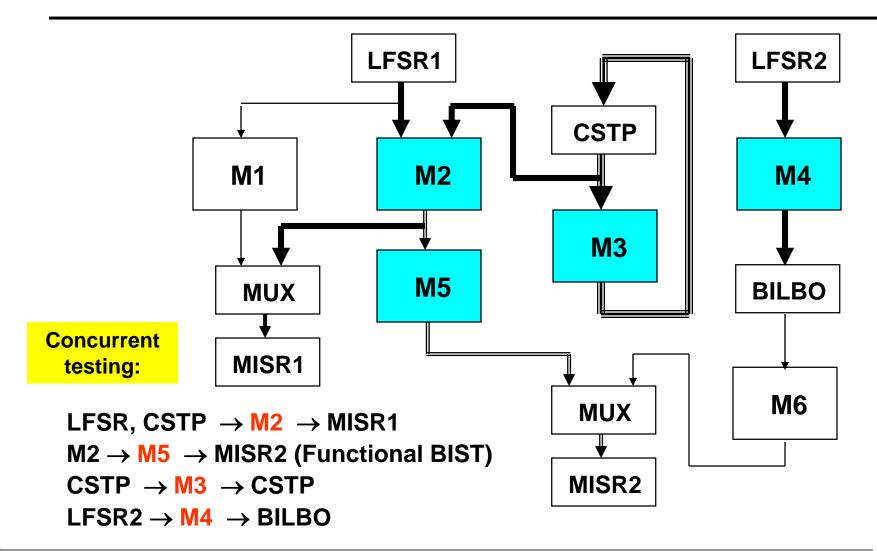

### **DFT for Random BIST & Functional BIST**

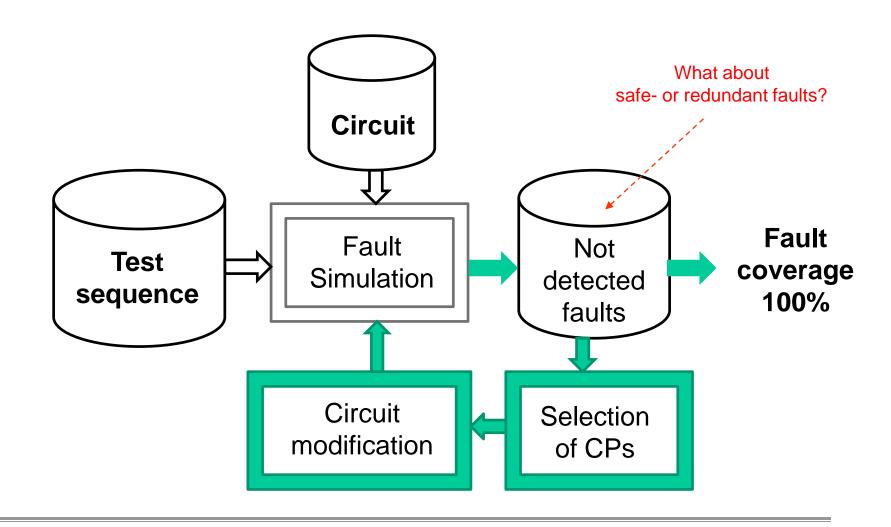

### **Selection of Test Points**

### **Test point selection approaches**

- Improving testability for any set of pseudo-random patterns (Pseudorandom BIST)

- Testability measures are used to characterize the controllability and observability of the circuit (independently of the test applied)

- Improving testability for a given implementation based sequence of vectors (Functional BIST)

- Fault simulation is used for measuring the fault coverage

#### Methods that are used:

- logic simulation,

- fault simulation,

- evaluation (measuring) of controllability and observability

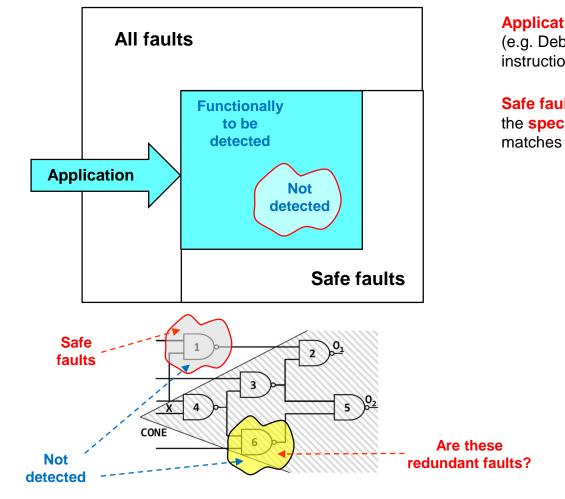

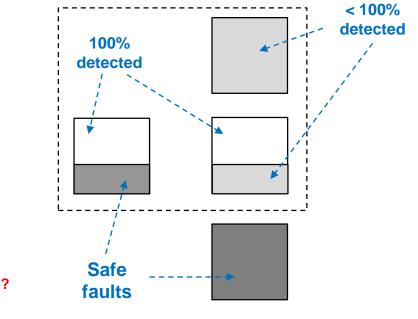

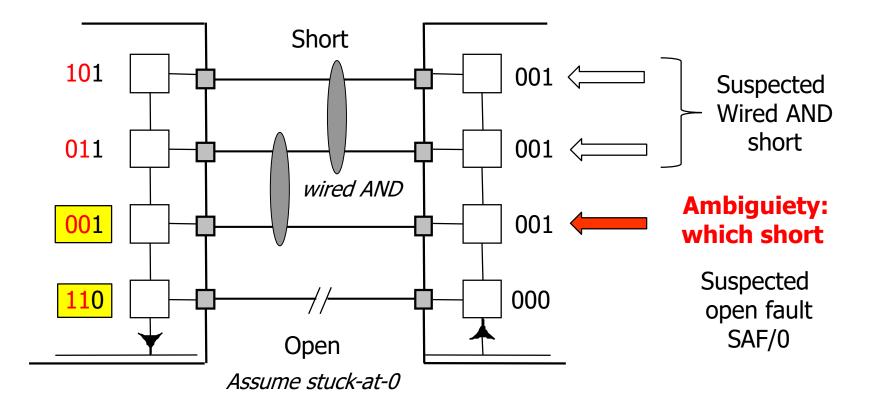

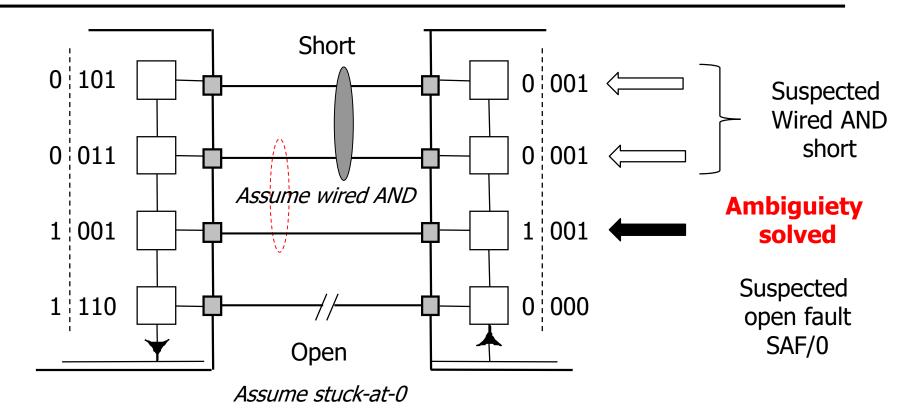

### The Problem of Safe/Redundant faults

**Application software** may not use a part of system HW (e.g. Debugging Module, Floating Point Unit), or a part of instruction set (e.g. multiplication)

Safe faults cannot produce any failure due to the specific (HW or SW) constraints the system matches during its normal operation

### **Adhoc Iterative DFT Improvement**

Technical University Tallinn, ESTONIA

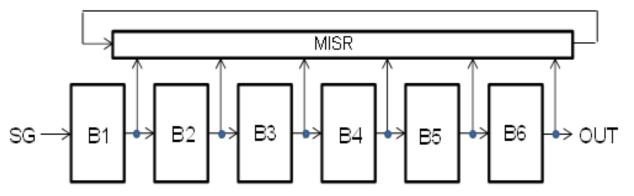

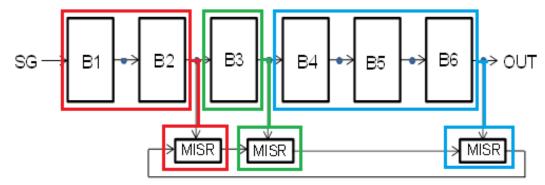

### **High-Level Functional BIST**

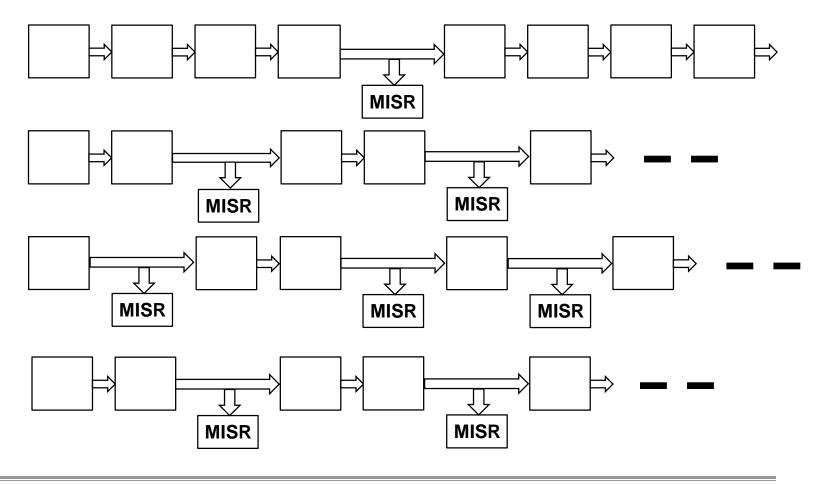

#### **Example: Functional BIST for Pipe-Lined Circuits**

#### **Two solutions**

MISR monitors on every register

MISR monitors on part of the register (Combine blocks with good coverage)

## **HL-FBIST Synthesis**

#### **Start-From-Big method**

## **HL-FBIST Synthesis**

#### **Start-From-Small method**

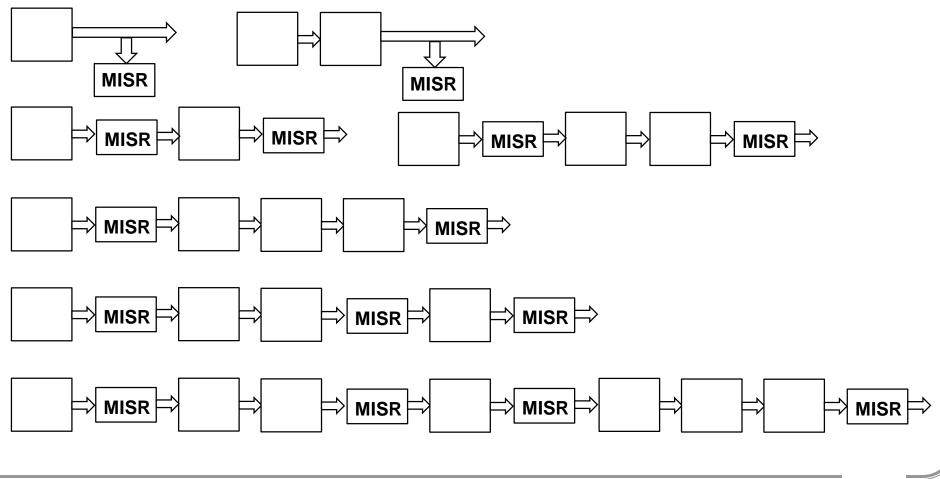

### **Distributed BIST Synthesis**

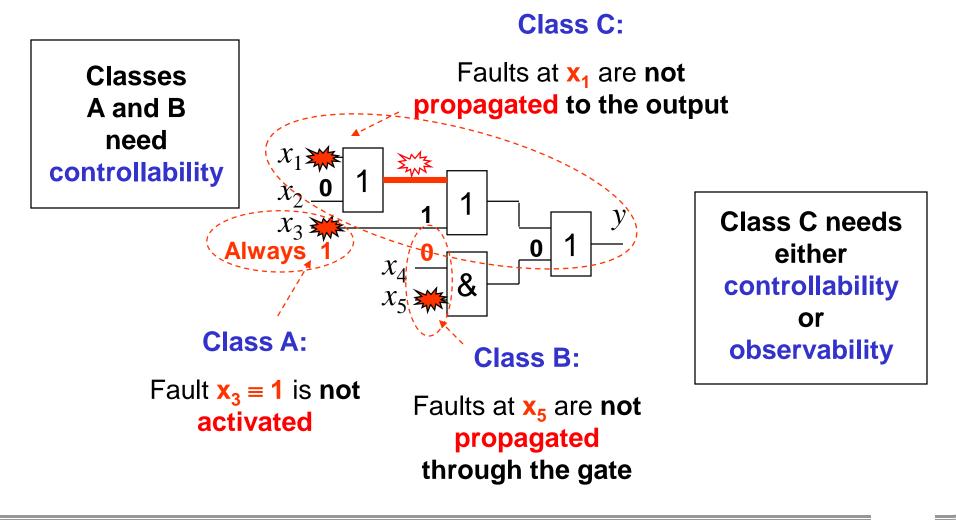

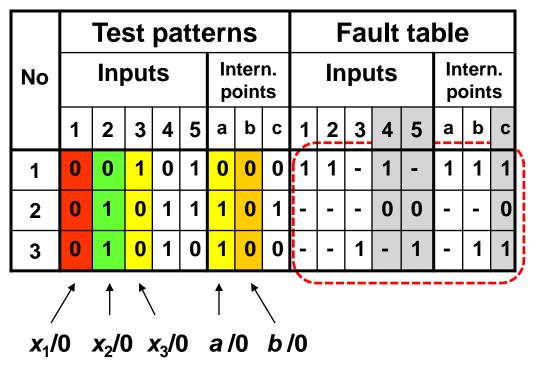

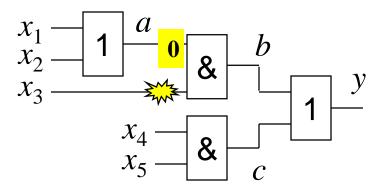

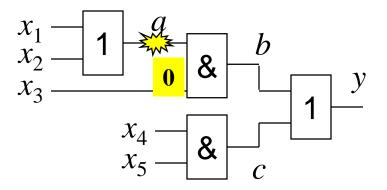

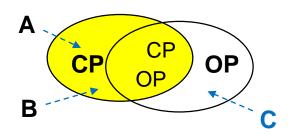

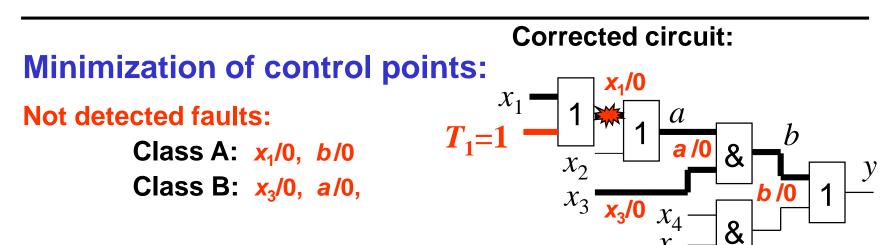

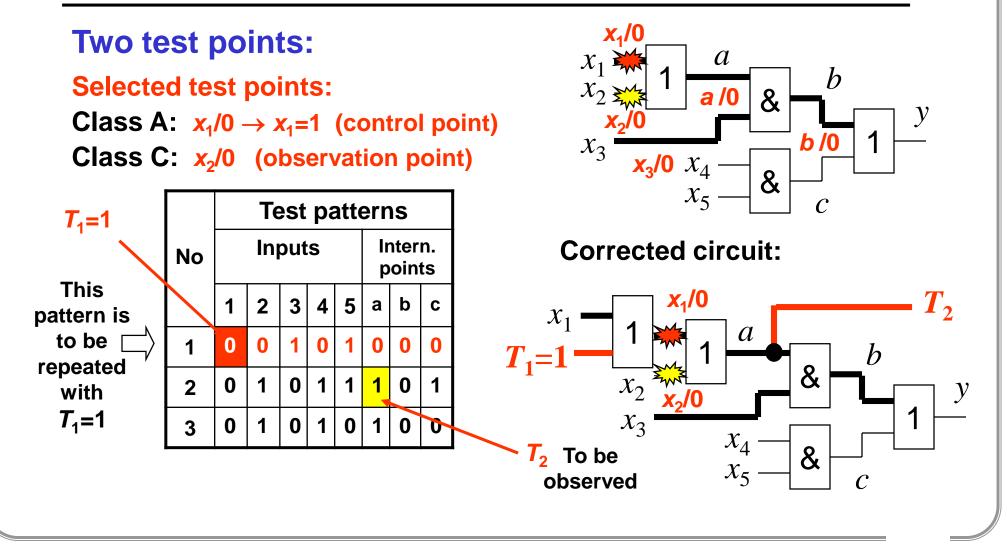

#### **Method: Simulation of given test patterns**

- Identification of the faults that are **detected**

- The remaining faults are classified as

- A: Faults that were not excited

- **B:** Faults at gate inputs that were excited but **not propagated to the <u>gate</u> output**

- C: Faults that were excited but not propagated to circuit output

- The faults A and B require control points for their detection

- The faults C may be detected by either by observation points or by control points

- Control points selection should be carried out before observation points selection

#### **Classification of Not-Detected Faults**

#### **Classification of faults**

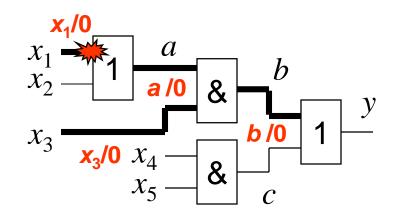

Given test:

Not detected faults:

| Class | Faults                    | Missing                      | signals    |

|-------|---------------------------|------------------------------|------------|

| Α     | <i>x</i> <sub>1</sub> /0: | <i>x</i> <sub>1</sub> = 1    | is missing |

| Α     | b/0:                      | b = 1                        | is missing |

| В     | <i>x</i> <sub>3</sub> /0: | <i>x</i> <sub>3</sub> a = 11 | is missing |

| В     | <i>a  </i> 0:             | <i>x</i> <sub>3</sub> a = 11 | is missing |

| С     | <i>x</i> <sub>2</sub> /0: | $x_1 x_2 = 01$               | ΟΚ         |

**Classification of faults**

**Class Faults Missing signals**

|   | <i>x</i> <sub>1</sub> /0: | <i>x</i> <sub>1</sub> = 1 | is missing |

|---|---------------------------|---------------------------|------------|

| • | <i>b</i> /0:              | b = 1                     | is missing |

| 3 | x <sub>3</sub> /0:        |                           | is missing |

| 3 | <i>a  </i> 0:             | $x_3 a = 11$              | is missing |

|   | <i>x</i> <sub>2</sub> /0: | $x_1 x_2 = 01$            | OK         |

#### **Classification of faults**

Given test:

|                       |        | Test patte |          |                   |   |          | rns Fault table |         |   |   |                   | e |   |   |   |   |

|-----------------------|--------|------------|----------|-------------------|---|----------|-----------------|---------|---|---|-------------------|---|---|---|---|---|

| No                    | Inputs |            |          | Intern.<br>points |   | Inputs   |                 |         |   |   | Intern.<br>points |   |   |   |   |   |

|                       | 1      | 2          | 3        | 4                 | 5 | а        | b               | С       | 1 | 2 | 3                 | 4 | 5 | а | b | С |

| 1                     | 0      | 0          | 1        | 0                 | 1 | 0        | 0               | 0       | 1 | 1 | -                 | 1 | - | 1 | 1 | 1 |

| 2                     | 0      | 1          | 0        | 1                 | 1 | 1        | 0               | 1       | - | - | -                 | 0 | 0 | - | - | 0 |

| 3                     | 0      | 1          | 0        | 1                 | 0 | 1        | 0               | 0       | - | - | 1                 | - | 1 | - | 1 | 1 |

| /<br>x <sub>1</sub> / | /<br>0 | ↑<br>x₂/(  | ^<br>د 0 | ر <sub>ع</sub> /۲ | ) | ↑<br>a / | ×<br>0          | \<br>b/ | 0 |   |                   |   |   |   |   |   |

#### Not detected faults:

| Class | -                             | Missing                      | •                        |

|-------|-------------------------------|------------------------------|--------------------------|

| Α     | <i>x</i> <sub>1</sub> /0:     | $x_1 = 1$                    | is missing<br>is missing |

| Α     | <i>b</i> /0:                  | b = 1                        | is missing               |

| В     | <mark>x<sub>3</sub>/0:</mark> | <i>x</i> <sub>3</sub> a = 11 | is missing               |

| В     | <i>a  </i> 0:                 | <i>x</i> <sub>3</sub> a = 11 | is missing               |

| С     | <i>x</i> <sub>2</sub> /0:     | $x_1 x_2 = 01$               | OK                       |

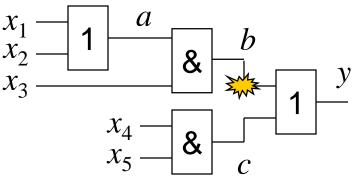

#### **Classification of faults**

Given test:

|                         |        | Test patte             |     |                   |                   |    | rns Fault table |   |    |   |   |                   |   |   |   |   |

|-------------------------|--------|------------------------|-----|-------------------|-------------------|----|-----------------|---|----|---|---|-------------------|---|---|---|---|

| No                      | Inputs |                        |     |                   | Intern.<br>points |    | Inputs          |   |    |   |   | Intern.<br>points |   |   |   |   |

|                         | 1      | 2                      | 3   | 4                 | 5                 | а  | b               | С | 1  | 2 | ვ | 4                 | 5 | а | b | С |

| 1                       | 0      | 0                      | 1   | 0                 | 1                 | 0  | 0               | 0 | 1  | 1 | - | 1                 | - | 1 | 1 | 1 |

| 2                       | 0      | 1                      | 0   | 1                 | 1                 | 1  | 0               | 1 | -  | - | - | 0                 | 0 | - | - | 0 |

| 3                       | 0      | 1                      | 0   | 1                 | 0                 | 1  | 0               | 0 | -  | - | 1 | -                 | 1 | - | 1 | 1 |

|                         | 1      | Î                      | 1   | \<br>\            |                   | 1  | ۲               |   |    |   |   |                   |   |   |   |   |

| <b>x</b> <sub>1</sub> / | 0      | <b>x<sub>2</sub>/(</b> | 0 3 | x <sub>3</sub> /( | D                 | a/ | 0               | b | /0 |   |   |                   |   |   |   |   |

#### Not detected faults:

| Class | Faults                    | Missing                      | signals    |

|-------|---------------------------|------------------------------|------------|

| Α     | <i>x</i> <sub>1</sub> /0: | <i>x</i> <sub>1</sub> = 1    | is missing |

| Α     | b/0:                      | b = 1                        | is missing |

| В     | x <sub>3</sub> /0:        | <i>x</i> <sub>3</sub> a = 11 | is missing |

| В     | <mark>a /0:</mark>        | <i>х</i> <sub>3</sub> а = 11 | is missing |

| С     | <i>x</i> <sub>2</sub> /0: | $x_1 x_2 = 01$               | OK         |

#### **Classification of faults**

Given test:

|                         |   | Test patte               |     |                          |   |                   | rns Fault tabl |        |    |   |   | ble               | ble |   |   |   |

|-------------------------|---|--------------------------|-----|--------------------------|---|-------------------|----------------|--------|----|---|---|-------------------|-----|---|---|---|

| No                      |   | Inputs                   |     |                          |   | Intern.<br>points |                | Inputs |    |   |   | Intern.<br>points |     |   |   |   |

|                         | 1 | 2                        | 3   | 4                        | 5 | а                 | b              | С      | 1  | 2 | 3 | 4                 | 5   | а | b | С |

| 1                       | 0 | 0                        | 1   | 0                        | 1 | 0                 | 0              | 0      | 1  | 1 | - | 1                 | -   | 1 | 1 | 1 |

| 2                       | 0 | 1                        | 0   | 1                        | 1 | 1                 | 0              | 1      | -  | - | - | 0                 | 0   | - | - | 0 |

| 3                       | 0 | 1                        | 0   | 1                        | 0 | 1                 | 0              | 0      | -  | - | 1 | -                 | 1   | - | 1 | 1 |

| /<br>v /                | 1 |                          |     |                          | n | 1                 | <u>م</u>       | \<br>b | /∩ |   |   |                   |     |   |   |   |

| <b>x</b> <sub>1</sub> / | 0 | <b>x</b> <sub>2</sub> /( | 0 3 | <b>x</b> <sub>3</sub> /( | 0 | a/                | 0              | b      | /0 |   |   |                   |     |   |   |   |

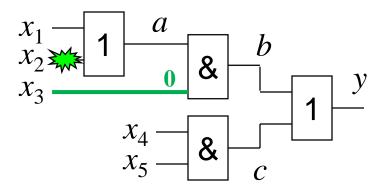

#### Not detected faults:

| Class | Faults                    | Missing                      |              |

|-------|---------------------------|------------------------------|--------------|

| Α     | <b>x</b> <sub>1</sub> /0: | <i>x</i> <sub>1</sub> = 1    | is missing   |

| Α     | b/0:                      | b = 1                        | is missing   |

| В     | <b>x</b> <sub>3</sub> /0: | <i>x</i> <sub>3</sub> a = 11 | is missing   |

| В     | <i>a  </i> 0:             | $x_3 a = 11$                 | is missing   |

| С     | <i>x</i> <sub>2</sub> /0: | $x_1 x_2 = 01$               | OK, but      |

| ľ     | path a                    | ctivation x <sub>(</sub>     | 3 is missing |

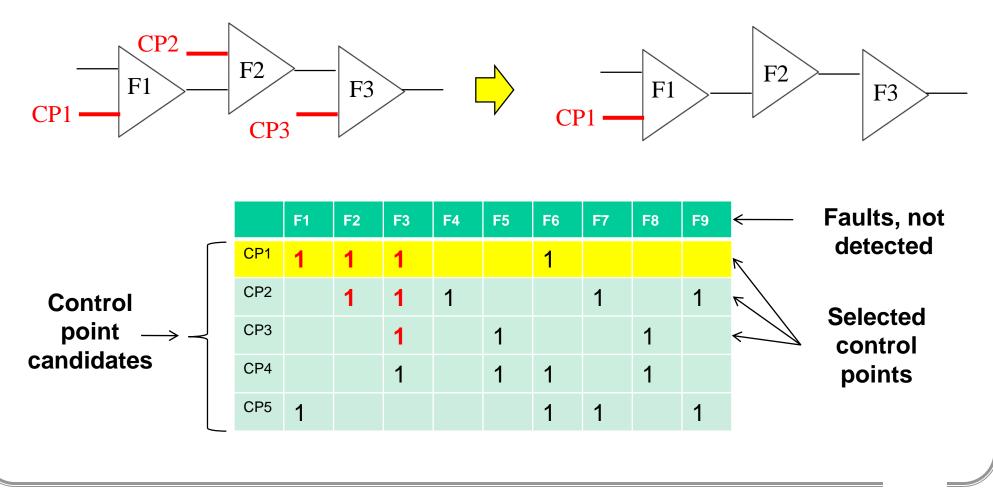

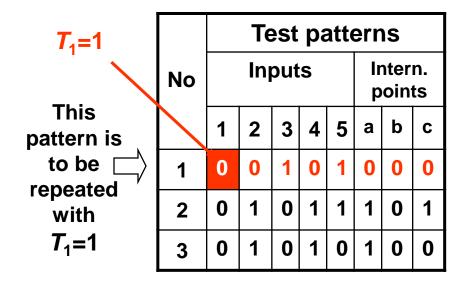

**1. Selection of control points:**

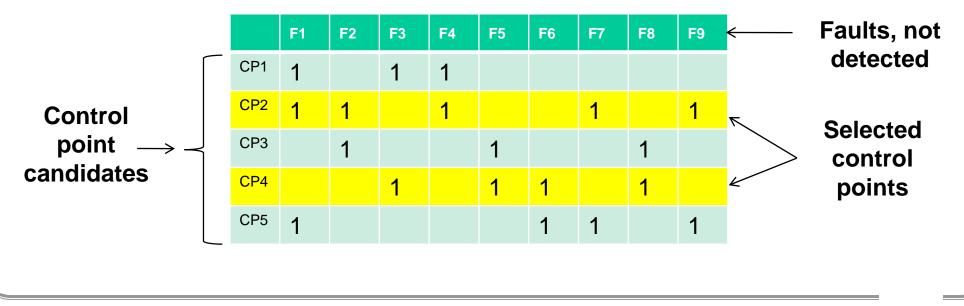

#### **1. Selection of control points:**

- Once control point candidates are identified for the faults A and B, a minimum number of control points (CP) can be identified

- This can be formulated as a minimum coverage problem where a minimum CPs are selected such that at least one CP candidate is included for each fault in A and B

#### **1. Selection of observation points:**

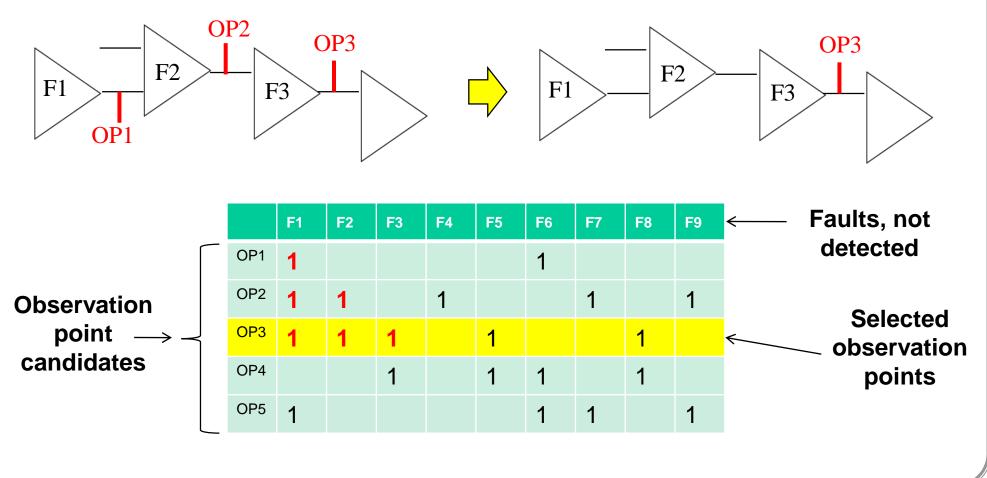

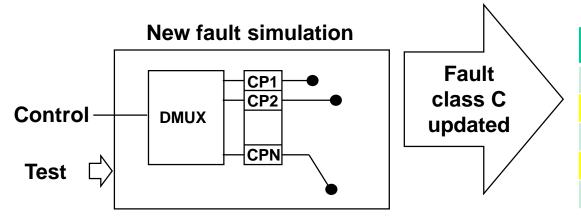

#### 2. Selection of observation points

- Once CPs selected, the test patterns are augmented, fault simulation is performed

- The fault class C is updated

- For each fault, in C the circuit lines to which the effect of the fault propagates, are identified as a potential observation point candidates

- A minimum covering problem is formulated and solved to find the observation points to be added

#### Minimization of observation points

|     | F1 | F2 | F3 | F4 | F5 | F6 | F7 | F8 | F9 |

|-----|----|----|----|----|----|----|----|----|----|

| OP1 | 1  |    | 1  | 1  |    |    |    |    |    |

| OP2 | 1  | 1  |    | 1  |    |    | 1  |    | 1  |

| OP3 |    | 1  |    |    | 1  |    |    | 1  |    |

| OP4 |    |    | 1  |    | 1  | 1  |    | 1  |    |

| OP5 | 1  |    |    |    |    | 1  | 1  |    | 1  |

#### **Control point coverage:**

| To be select      | ed                       | Not de                   | tected                   | faults       |     |

|-------------------|--------------------------|--------------------------|--------------------------|--------------|-----|

|                   |                          | <i>x</i> <sub>1</sub> /0 | <i>x</i> <sub>3</sub> /0 | <i>a  </i> 0 | b/0 |

|                   | <i>x</i> <sub>1</sub> =1 | +                        | +                        | +            | +   |

| Potential control | <i>x</i> <sub>3</sub> =1 |                          | +                        | +            | +   |

| points            | a=1                      |                          | +                        | +            | +   |

|                   | b=1                      |                          |                          |              | +   |

|    |   | Те                       | erns |   |   |   |   |   |  |

|----|---|--------------------------|------|---|---|---|---|---|--|

| No |   | Inputs Intern.<br>points |      |   |   |   |   |   |  |

|    | 1 | 2                        | 5    | a | b | С |   |   |  |

| 1  | 0 | 0                        | 1    | 0 | 1 | 0 | 0 | 0 |  |

| 2  | 0 | 1                        | 0    | 1 | 1 | 1 | 0 | 1 |  |

| 3  | 0 | 1                        | 0    | 1 | 0 | 1 | 0 | 0 |  |

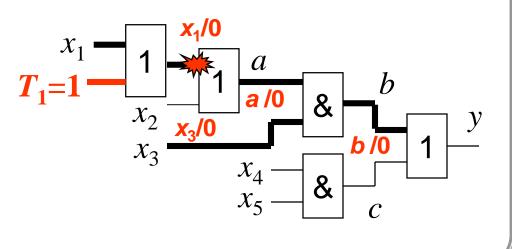

#### **Insertion of Test Points**

#### Test point for $x_1/0$

#### All faults detected:

Class A:  $x_1/0$ , b/0Class B:  $x_3/0$ , a/0,

#### **Corrected circuit:**

### **Insertion of Test Points**

### **Selection of Test Points – Tradeoff Problem**

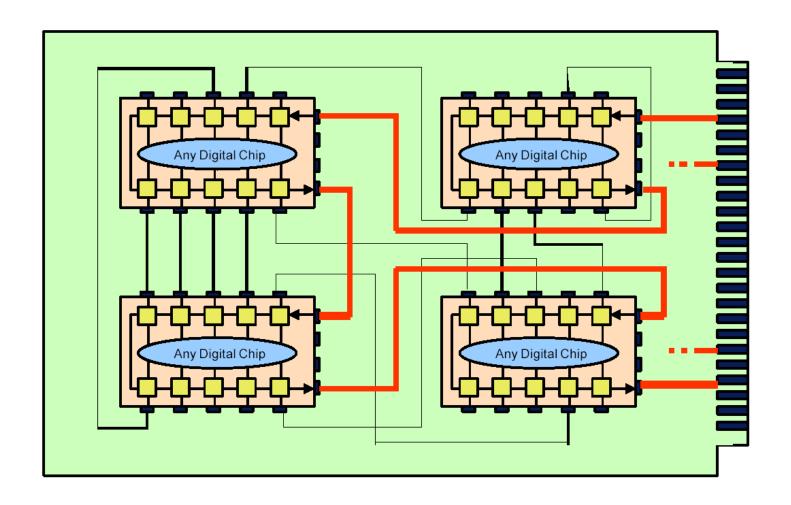

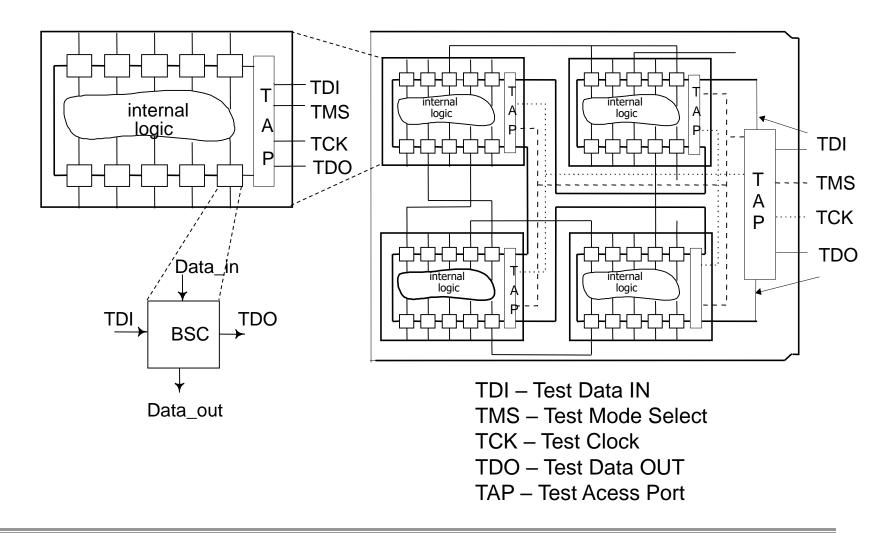

#### **Boundary Scan Standard**

#### **Boundary Scan Architecture**

#### **Boundary Scan Architecture**

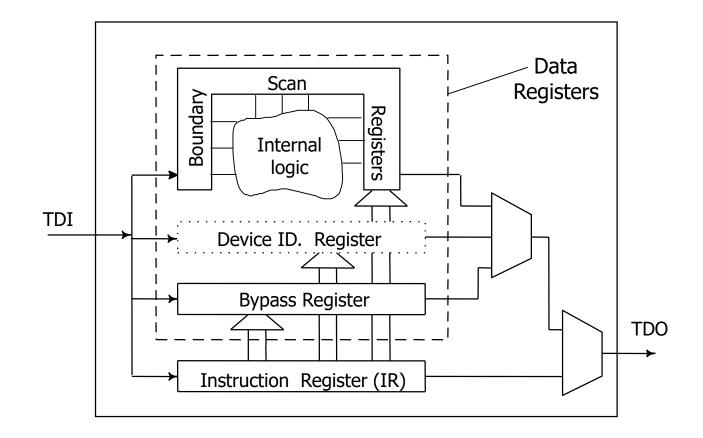

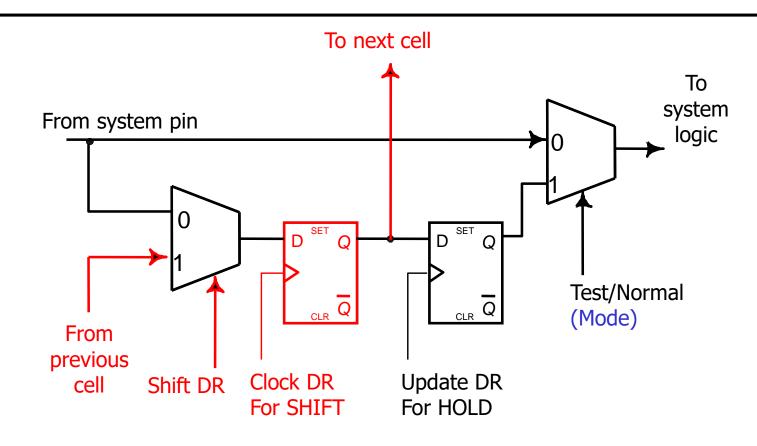

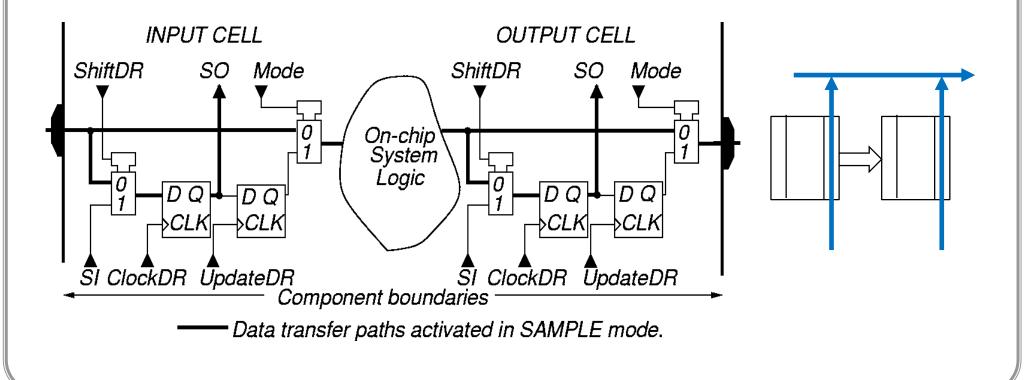

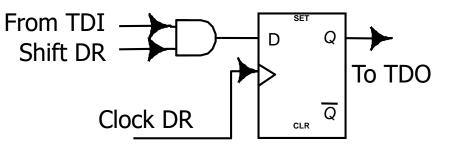

# **Boundary Scan Cell**

Used at the input or output pins

#### **SAMPLE mode:**

Get snapshot of normal chip output signals (monitoring mode)

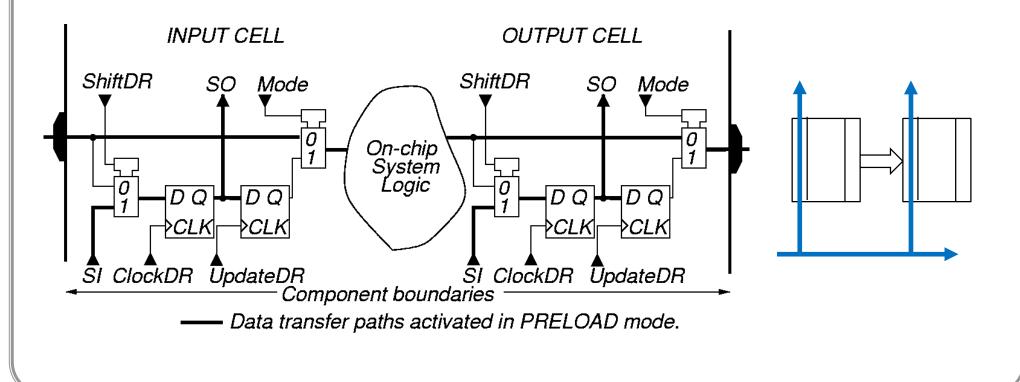

#### **PRELOAD mode:**

Put data on boundary scan chain before next instruction

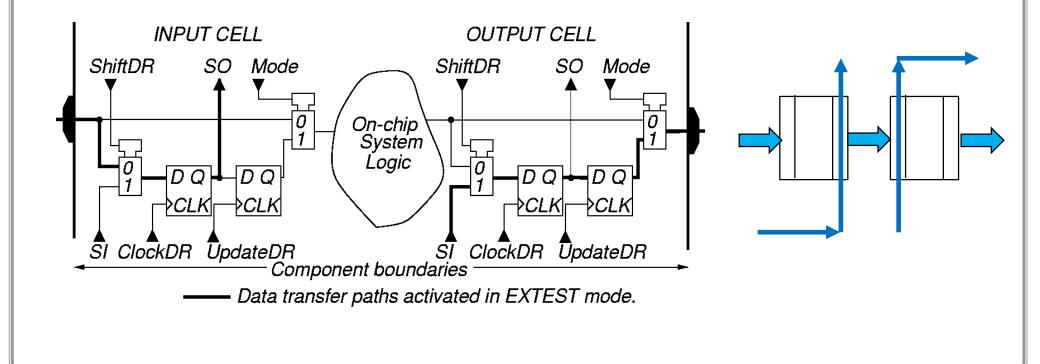

#### **EXTEST** instruction:

Test off-chip circuits and board-level interconnections

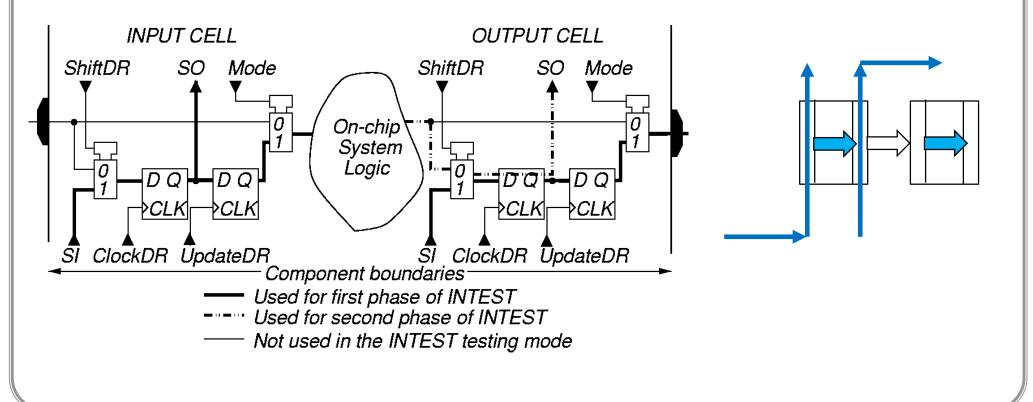

#### **INTEST** instruction

Feeds external test patterns in and shifts responses out

#### **Bypass instruction:**

Bypasses the corresponding chip using 1-bit register

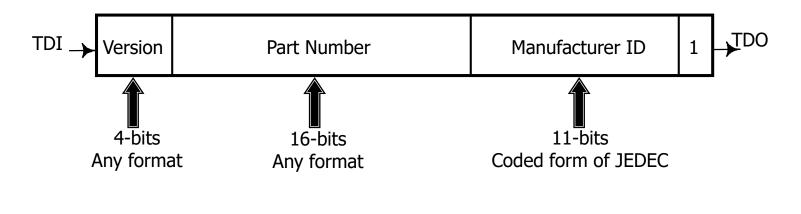

#### **IDCODE** instruction:

Connects the component device identification register serially between TDI and TDO in the Shift-DR TAP controller state

Allows board-level test controller or external tester to read out component ID

**Required** whenever a JEDEC identification register is included in the design

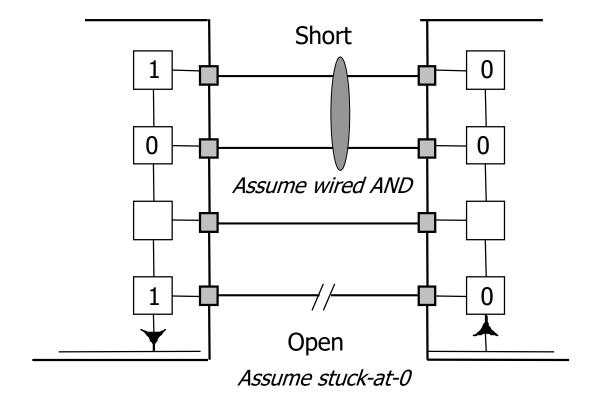

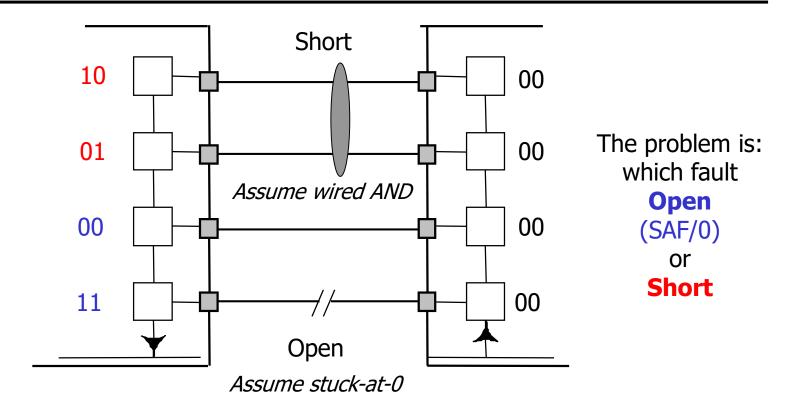

#### **Fault Detection with Boundary Scan**

### **Any Bridge Detection with Boundary Scan**

Kautz showed in 1974 that a sufficient condition to detect any pair of short circuited nets was that the "horizontal" codes must be unique for all nets. Therefore the test length is  $log_2(N)$ [

# **Any Fault Detection with Boundary Scan**

All 0-s and all 1-s are forbidden codes because of stuck-at faults Therefore the final test length is  $log_2(N+2)[$  (for testing SAF without masking by shorts)

# Fault Diagnosis with Boundary Scan

To improve the diagnostic resolution we have to add one bit more

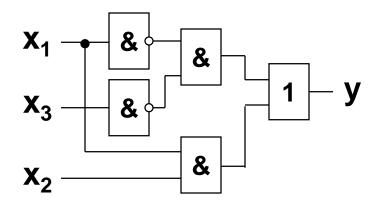

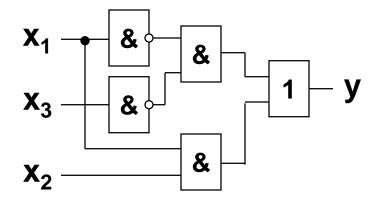

y

$y = x_1 x_3 \lor x_1 x_2$

#### **Test generation:**

| $=\overline{x_1}$   | $\overline{x_3}$ | $\checkmark x_1$ | $X_2$ | <b>x</b> <sub>1</sub> | <b>X</b> <sub>2</sub> | <b>X</b> <sub>3</sub> | У |

|---------------------|------------------|------------------|-------|-----------------------|-----------------------|-----------------------|---|

| <mark>0</mark><br>1 | 1                | 1                | 0     | 1                     | 0<br>1                | 0                     | 0 |

| 1                   | 1                | 0                | 0     | 0                     | 0                     | 1                     | 1 |

| 0                   | 0                | 1                | 1     | 1                     | 1                     | 1                     | 1 |

|                     |                  |                  |       |                       |                       |                       |   |

#### 4 test patterns are needed

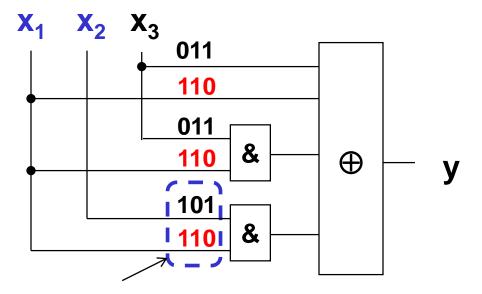

#### **Two implementations for the same circuit:**

$$y = x_1 x_3 \lor x_1 x_2$$

**Test generation start**

<u>Here:</u> 4 test patterns are needed <u>Here:</u> Only 3 test patterns are needed

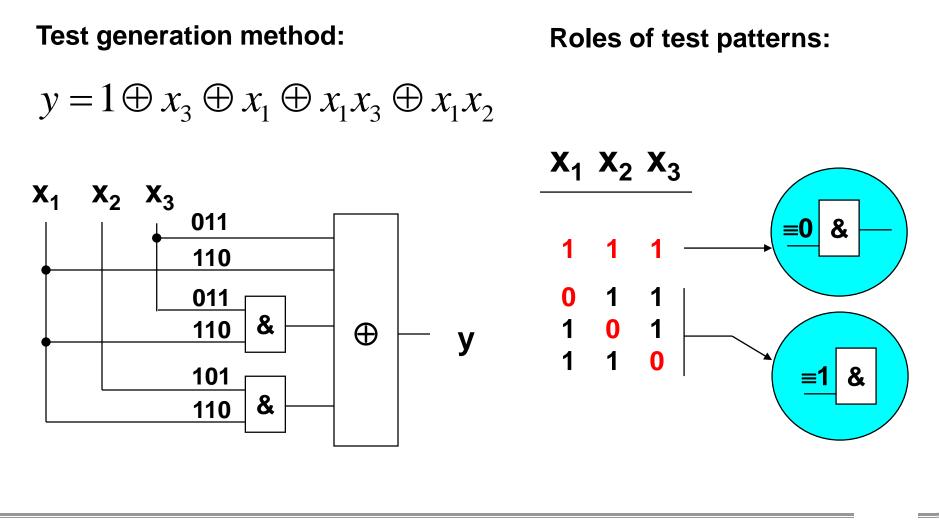

**Given:**  $y = x_1 x_3 \lor x_1 x_2$

$y = c_0 \oplus c_1 x_3 \oplus c_2 x_2 \oplus c_3 x_2 x_3 \oplus c_4 x_1 \oplus c_5 x_1 x_3 \oplus c_6 x_1 x_2 \oplus c_7 x_1 x_2 x_3$

**Calculation of constants:**

| f <sub>i</sub>        | <b>X</b> <sub>1</sub> | <b>X</b> <sub>2</sub> | <b>X</b> <sub>3</sub> | У | Σ | New circuit:                                                                                                                                                                  |

|-----------------------|-----------------------|-----------------------|-----------------------|---|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f <sub>o</sub>        | 0                     | 0                     | 0                     | 1 | 1 | $\mathbf{C}_{0} = \mathbf{f}_{0} = 1 \qquad \qquad$    |

| f <sub>1</sub>        | 0                     | 0                     | 1                     | 0 | 1 | $\mathbf{C}_1 = \mathbf{f}_0 \oplus \mathbf{f}_1 = 1$                                                                                                                         |

| $\mathbf{f}_2$        | 0                     | 1                     | 0                     | 1 | 0 | $\mathbf{C}_2 = \mathbf{f}_0 \oplus \mathbf{f}_2 = 0$                                                                                                                         |

| $\mathbf{f}_3^-$      | 0                     | 1                     | 1                     | 0 | 0 | $\mathbf{C}_3 = \mathbf{f}_0 \oplus \mathbf{f}_1 \oplus \mathbf{f}_2 \oplus \mathbf{f}_3 = 0$                                                                                 |

| $\mathbf{f}_4$        | 1                     | 0                     | 0                     | 0 | 1 | $C_4 = f_0 \oplus f_4 = 1$                                                                                                                                                    |

| $f_5$                 | 1                     | 0                     | 1                     | 0 | 0 | $C_5 = f_0 \oplus f_1 \oplus f_4 \oplus f_5 = 1$                                                                                                                              |

| f <sub>6</sub>        | 1                     | 1                     | 0                     | 1 | 1 | $C_6 = f_0 \oplus f_2 \oplus f_4 \oplus f_6 = 1$                                                                                                                              |

| <b>f</b> <sub>7</sub> | 1                     | 1                     | 1                     | 1 | 0 | $\mathbf{C}_7 = \mathbf{f}_0 \oplus \mathbf{f}_1 \oplus \mathbf{f}_2 \oplus \mathbf{f}_3 \oplus \mathbf{f}_4 \oplus \mathbf{f}_5 \oplus \mathbf{f}_6 \oplus \mathbf{f}_7 = 0$ |