# Chapter 8

# **LCD Controller**

The Liquid Crystal Display (LCD) controller, which is incorporated into several devices in the MSP430 family ('3xx and '4xx), provides a rapid and simple way to interface between a program and an LCD display. The LCD controller controls the LCD display, generating voltage signals for the segments. It supports static and multiplexed display interfaces (2 mux, 3 mux and 4 mux). This chapter describes in detail the LCD driver interface and LCD\_A controller, both of which are implemented in the MSP430FG4618 device on the Experimenter's board.

| Topic                                               | Page |

|-----------------------------------------------------|------|

| 8.1 LCD Controller Introduction                     | 8-3  |

| 8.1.1 Main differences between LCD and LCD_A contro |      |

| 8.2 LCD_A Controller Operation                      | 8-3  |

| 8.2.1 LCD Memory                                    | 8-4  |

| 8.2.2 Blinking the LCD                              | 8-5  |

| 8.2.3 LCD_A Voltage and Bias Generation             | 8-5  |

| LCD Voltage Selection                               | 8-6  |

| LCD Bias Generation                                 | 8-6  |

| 8.2.4 LCD Contrast Control                          | 8-6  |

| 8.2.5 LCD Timing Generation                         | 8-7  |

| 8.3 LCD modes                                       | 8-7  |

| 8.3.1 Static Mode                                   | 8-7  |

| 8.3.2 2-Mux Mode                                    | 8-8  |

| 8.3.3 3-Mux Mode8                                   | -10  |

| 8.3.4 4-Mux Mode8                                   | -11  |

| 8.4 | Registers                              | 8-12 |

|-----|----------------------------------------|------|

| 8.5 | Laboratory 4: LCD message presentation | 8-14 |

| 8.6 | Quiz                                   | 8-20 |

| 8.7 | FAQs                                   | 8-21 |

|     |                                        |      |

# 8.1 LCD Controller Introduction

The LCD controllers supported by the '3xx and '4xx families drive LCD displays with a range of multiplex rates. Two LCD controllers are supported by the MSP430 microcontroller family. The first, known as the LCD controller, is supported by all MSP430x4xx devices. The second, known as LCD\_A, is supported by the MSP430x42x0 and MSP430FG461x devices.

This chapter will focus on the operation of the LCD\_A controller, because it is the one used by the MSP430FG4618 MCU fitted on the Experimenter's board.

Both LCD controllers include the following features:

- □ Display memory;

- □ Automatic signal generation;

- □ Configurable frame frequency;

- Blinking capability;

- □ Support for 4 types of LCDs:

- Static;

- 2-mux, 1/2 bias (or 1/3 bias for LCD\_A controller);

- 3-mux, 1/3 bias (or 1/2 bias for LCD\_A controller);

- 4-mux, 1/3 bias (or 1/2 bias for LCD\_A controller).

## 8.1.1 Main differences between LCD and LCD\_A controllers

The main differences between the two LCD controllers relate to their features. The LCD\_A provides a regulated charge pump and allows contrast control by software. Additionally, for this driver, fractional LCD biasing voltages can be sourced internally or externally. The LCD controller requires external circuitry (a resistor-divider network) to generate up to 4 externally driven voltage levels (R03, R13, R23 and R33), which source the internal voltage generator.

With respect to the timing generator, the differences arise from the clock signal used for the LCD frequency. Whilst the LCD controller uses the timing generator sourced from Basic Timer 1 (see Chapter 8), the LCD\_A controller uses ACLK to generate the timing for common and segment lines.

# 8.2 LCD\_A Controller Operation

The LCD\_A controller can be configured as the controller for the LCD, making use of external circuitry (a resistor-divider network). This generates up to 4 externally supplied voltage levels (R03, R13, R23 and R33), which source the voltage generators, V5, V4 and V3, V2 and V1 respectively. Additionally, the LCD Bias Generator can internally generate the fractional LCD biasing voltages, V2 – V5, independent of the source of  $V_{LCD}$ :

- R33  $\rightarrow$  V1: full-scale voltage (V<sub>LCD</sub>);

- R23  $\rightarrow$  V2: 2/3 of full scale;

- V3: 1/2 of full scale (LCD\_A controller only);

- R13  $\rightarrow$  V4: 1/3 of full scale;

- **R**03  $\rightarrow$  V5: ground.

The following table gives the LCD Voltage and Biasing Characteristics of the LCD\_A controller:

Table 8-1. LCD\_A controller naming convention, LCD Voltage and Biasing Characteristics.

| Mode   | Bias conf. |        | LCD_A controller |     |    |    |    |    |    |

|--------|------------|--------|------------------|-----|----|----|----|----|----|

|        |            | LCDMXx | LCD2B            | COM | V1 | V2 | V3 | V4 | V5 |

| Static | Static     | 00     | Х                | 1   | Х  |    |    |    | Х  |

| 2-mux  | 1/2        | 01     | 1                | 2   | Х  |    | Х  |    | Х  |

| 2-mux  | 1/3        | 01     | 0                | 2   | Х  | Х  |    | Х  | Х  |

| 3-mux  | 1/2        | 10     | 1                | 3   | Х  |    | Х  |    | Х  |

| 3-mux  | 1/3        | 10     | 0                | 3   | Х  | Х  |    | Х  | Х  |

| 4-mux  | 1/2        | 11     | 1                | 4   | Х  |    | Х  |    | Х  |

| 4-mux  | 1/3        | 11     | 0                | 4   | Х  | Х  |    | Х  | Х  |

Although LCD and LCD\_A controllers use different clock signals to source the timing generator, the LCD\_A circuit sources the analogue voltage multiplexer that generates the control signals for the multiplexers.

Because the LCD\_A controller uses the user selectable ACLK (32768 Hz) prescaler, selected with the LCDFREQx bits, the appropriate LCD frequency,  $f_{LCD}$ , depends on the framing frequency,  $f_{frame}$ , and multiplex rate, mux, defined on the LCD specifications. The LCD frequency should be configured according to the following equation:

$f_{LCD} = 2 \times mux \times f_{frame}$

## 8.2.1 LCD Memory

8-4

The LCD memory map is shown in *Figure* 8-1. Depending on the LCD type (Static, 2-mux, 3-mux or 4-mux) and on the device, each LCD segment is turned on by setting its corresponding memory bit.

The maximum number of segment lines available depends on the device. Refer to the appropriate device-specific data sheet for the available segment pins.

Figure 8-1. LCD Memory Map.

| Associated<br>Common Pins | 3 | 2  | 1  | 0 | 3  | 2 | 1 | 0 | <u>م</u> | ssociated   |

|---------------------------|---|----|----|---|----|---|---|---|----------|-------------|

| Address                   | 7 |    |    |   |    |   |   | 0 | n Se     | egment Pins |

| 0A4h                      |   |    |    |   |    |   |   |   | 38       | 39, 38      |

| 0A3h                      |   |    |    |   |    |   |   |   | 36       | 37, 36      |

| 0A2h                      |   |    |    |   |    |   |   |   | 34       | 35, 34      |

| 0A1h                      |   |    |    |   |    |   |   |   | 32       | 33, 32      |

| 0A0h                      |   |    |    |   |    |   |   |   | 30       | 31, 30      |

| 09Fh                      |   |    |    |   |    |   |   |   | 28       | 29, 28      |

| 09Eh                      |   |    |    |   |    |   |   |   | 26       | 27, 26      |

| 09Dh                      |   |    |    |   |    |   |   |   | 24       | 25, 24      |

| 09Ch                      |   |    |    |   |    |   |   |   | 22       | 23, 22      |

| 09Bh                      |   |    |    |   |    |   |   |   | 20       | 21, 20      |

| 09Ah                      |   |    |    |   |    |   |   |   | 18       | 19, 18      |

| 099h                      |   |    |    |   |    |   | - |   | 16       | 17, 16      |

| 098h                      |   |    |    |   |    |   |   |   | 14       | 15, 14      |

| 097h                      |   |    |    |   |    |   |   |   | 12       | 13, 12      |

| 096h                      |   |    |    |   |    |   |   |   | 10       | 11, 10      |

| 095h                      |   |    |    |   |    |   |   |   | 8        | 9, 8        |

| 094h                      |   |    |    |   |    |   |   |   | 6        | 7, 6        |

| 093h                      |   |    |    |   |    |   |   |   | 4        | 5, 4        |

| 092h                      |   |    |    |   |    |   |   |   | 2        | 3, 2        |

| 09 <b>1</b> h             |   |    |    |   |    |   |   |   | 0        | 1, 0        |

|                           |   |    |    |   | `\ |   |   |   | r        |             |

|                           |   | Sn | +1 |   |    | S | n |   |          |             |

#### 8.2.2 Blinking the LCD

The LCD controller supports blinking. The LCDSON bit is ANDed with the memory bit of each segment. When LCDSON = 1, each segment is on or off, depending on the value of its memory bit. When LCDSON = 0, each LCD segment is turned off.

#### 8.2.3 LCD\_A Voltage and Bias Generation

In addition to internal voltage generation, both the peak output waveform voltage, V1, as well as the fractional LCD biasing voltages V2 – V5 can be sourced externally.

- □ To use the internal voltage generator:

- OSCOFF = 1: Oscillator sourcing ACLK set;

- LCDON = 1: LCD\_A module active;

- $\circ~V_{\text{LCD}}$  may be sourced internally from  $AV_{\text{CC}}$  or from an internal charge pump.

- $\Box$  To source V<sub>LCD</sub> externally, the above bits must be disabled.

# **LCD Voltage Selection**

V<sub>LCD</sub> source:

- $\Box$  AV<sub>CC</sub> requires:

- VLCDEXT = 0;

- VLCDx = 0;

- VREFx = 0.

- $\hfill\square$  Internal charge pump sourced from  $\mathsf{DV}_{\mathsf{CC}}$  requires:

- VLCDEXT = 0;

- VLCDPEN = 1;

- VLCDx > 0 (software selectable LCD voltage from typically 2.60 V to 3.44 V: independent of DV<sub>CC</sub>);

- $\blacksquare$  Connect a 4.7  $\mu F$  or larger capacitor between pin LCDCAP and ground.

#### **LCD Bias Generation**

- □ Generation of external fractional LCD biasing voltages, V2 V5:

- REXT = 1;

- External equally weighted resistor divider network, with resistor values between 100 k $\Omega$  and 1 M $\Omega$ ;

- VLCDEXT = 0: The V<sub>LCD</sub> voltage is sourced from the internal charge pump, with R33 providing a switched-V<sub>LCD</sub> output. Otherwise (VLCDEXT = 1), R33 provides a V<sub>LCD</sub> input.

- R03EXT = 1: V5 is sourced externally.

- □ Internal bias generator:

- When LCD2B = 1, it supports 1/2 bias LCDs.

- When LCD2B = 0, it supports 1/3 bias LCDs in 2-mux, 3-mux, and 4-mux modes. In static mode, the internal divider network is disabled;

- For LCD devices that share the LCDCAP, R33, and R23 functions, the charge pump cannot be used with an external resistor divider with 1/3 biasing;

- When R03 is not available externally, V5 is always AV<sub>SS</sub>.

# 8.2.4 LCD Contrast Control

The VLCDx selection controls the LCD contrast by adjusting the LCD voltage generated by the integrated charge pump.

- □ The contrast of the LCD depends on the:

- Peak voltage of the output waveforms;

- Selected mode;

- Biasing.

- □ The contrast ratio of the LCD depends on the:

- LCD display;

- Selected biasing scheme.

### 8.2.5 LCD Timing Generation

$\Box$  LCD frequency,  $f_{LCD}$ , depends on the:

- Framing frequency;

- LCD multiplex rate;

- Selectable with the LCDFREQx bits.

$f_{LCD} = 2 \times mux \times f_{frame}$

# 8.3 LCD modes

The LCD\_A controller supports 4 types of LCD devices:

□ Static:

- Each MSP430 segment pin drives one LCD segment;

- One common line driven by COM0;

- Capacity to drive 32 segments.

- □ 2-mux, 1/2 bias (or 1/3 bias for LCD\_A controller):

- Each MSP430 segment pin drives two LCD segments;

- Two common lines driven by COM0 and COM1;

- Capacity to drive 64 segments.

- □ 3-mux, 1/3 bias (or 1/2 bias for LCD\_A controller):

- Each MSP430 segment pin drives three LCD segments;

- Three common lines driven by COM0, COM1, and COM2;

- Capacity to drive 90 segments.

- □ 4-mux, 1/3 bias (or 1/2 bias for LCD\_A controller):

- Each MSP430 segment pin drives four LCD segments

- Four common lines driven by COM0, COM1, COM2, and COM3;

- Capacity to drive 160 segments.

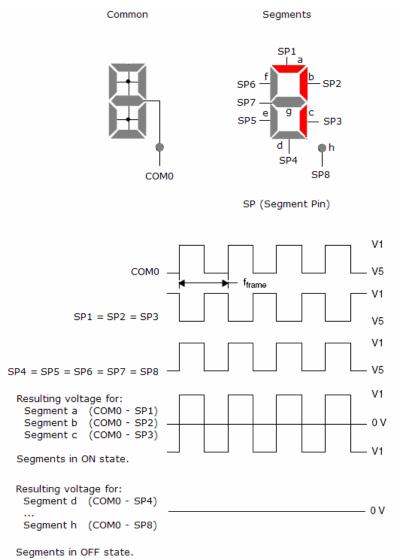

#### 8.3.1 Static Mode

A static LCD has one pin for each segment and one pin for the backplane. This type of LCD has a high contrast ratio but requires a large number of pins.

**Example:** Display the number "7" on the LCD

To display the number "7" on the LCD, segments a, b and c must be turned on. The waveforms at pins SP1, SP2 and SP3 (see *Figure 8*-

2), must be the inverse of the waveform at the common pin (COM0), so these segments are in the ON state. The waveforms at the remaining segment pins must be the same as the common pin waveform, to obtain the OFF state. *Figure* 8-2 shows an example of a static waveforms to display the number "7".

Figure 8-2. Static LCD waveforms – example: display number "7".

Additional details are given in the MSP430x4xx Family User's Guide <*slau056g.pdf*>.

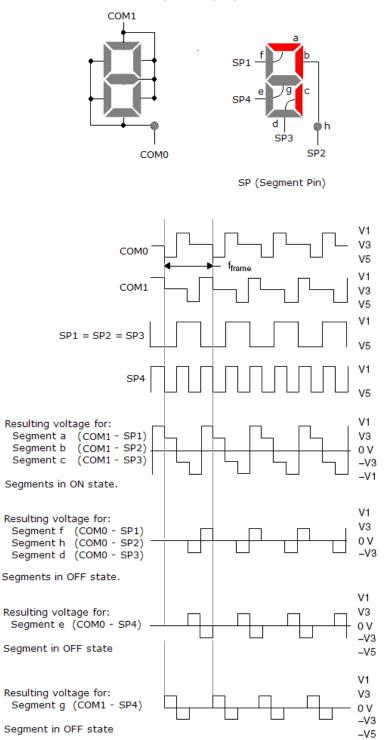

# 8.3.2 2-Mux Mode

To reduce the pin count, there are LCDs where the segments are multiplexed. In the case of a 2-mux LCD, the individual LCD segments are arranged in a matrix, with two common pins (COM0 and COM1). This type of LCD requires half the pin count of a static LCD.

#### Example: Display the number "7" on the LCD

To display the number "7" on the LCD, segments a, b and c must be turned on. The waveforms at pins, SP1, SP2 and SP3 (see Figure 7-3) must be time-division-multiplexed. The voltage signals that use combined common pins (COM0 or COM1) turn these segments ON by applying the voltage V1. The resulting voltage waveforms at the remaining segment pins must be lower than the LCD segment driving voltage (V1), in order to achieve the OFF state. *Figure 8–3* shows an example of 2-mux, 1/2 bias, waveforms for displaying the number "7".

Figure 8-3. 2-mux LCD waveforms – example: display number "7".

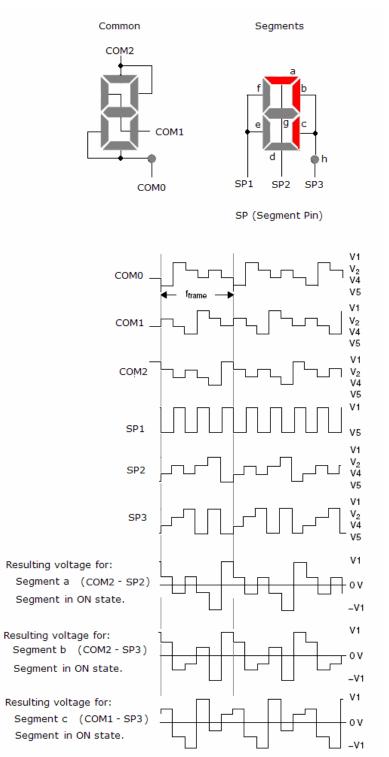

# 8.3.3 3-Mux Mode

In 3-mux mode, the MSP430 segment pins drive three LCD segments and three common lines (COM0, COM1, and COM2). This increases the number of available segments, without increasing the pin count. In *Figure 8-4* shows a 3-mux LCD waveform – example: the number "7".

The remaining segments are in the OFF state, producing different waveforms varying between -V4 and V4, with voltages that cannot drive the LCD.

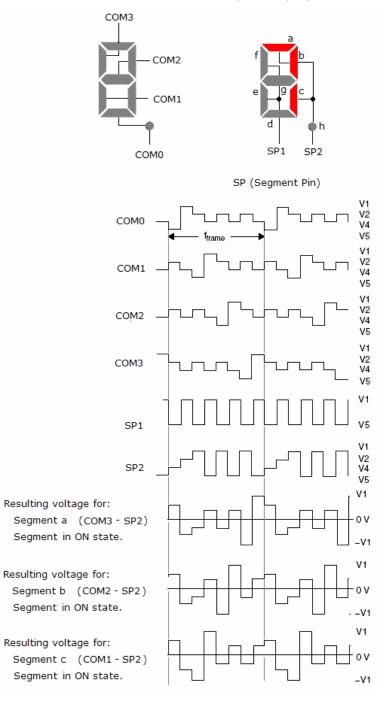

#### 8.3.4 4-Mux Mode

In 4-mux mode, the MSP430 segment pins drive four LCD segments and four common lines (COM0, COM1, COM2, and COM3).

*Figure 8–5* shows an example 4-mux, 1/3 bias LCD waveforms – example: number "7".

Figure 8-5. 4-mux LCD, 1/3 bias, waveforms – example: display number "7".

As in the previous example, the additional segments are in the OFF state, generating different waveforms varying between -V4 and V4 voltages that cannot drive the LCD.

# 8.4 Registers

# LCDACTL, LCD\_A Control Register

| 7 5      | 4  | 3    | 2      | 1      | 0     |

|----------|----|------|--------|--------|-------|

| LCDFREQx | LC | DMXx | LCDSON | Unused | LCDON |

| Bit   |          | Description                                         |            |

|-------|----------|-----------------------------------------------------|------------|

| 7 - 5 | LCDFREQx | LCD Frequency Select by ACLK divider configuration: |            |

|       |          | LCDFREQ2 LCDFREQ1 LCDFREQ0 = 000 $\Rightarrow$      | ACLK / 32  |

|       |          | LCDFREQ2 LCDFREQ1 LCDFREQ0 = 001 $\Rightarrow$      | ACLK / 64  |

|       |          | LCDFREQ2 LCDFREQ1 LCDFREQ0 = 010 $\Rightarrow$      | ACLK / 96  |

|       |          | LCDFREQ2 LCDFREQ1 LCDFREQ0 = 011 $\Rightarrow$      | ACLK / 128 |

|       |          | LCDFREQ2 LCDFREQ1 LCDFREQ0 = 100 $\Rightarrow$      | ACLK / 192 |

|       |          | LCDFREQ2 LCDFREQ1 LCDFREQ0 = 101 $\Rightarrow$      | ACLK / 256 |

|       |          | LCDFREQ2 LCDFREQ1 LCDFREQ0 = 110 $\Rightarrow$      | ACLK / 384 |

|       |          | LCDFREQ2 LCDFREQ1 LCDFREQ0 = 111 $\Rightarrow$      | ACLK / 512 |

| 4 - 3 | LCDMXx   | LCD mux rate for LCD mode setting:                  |            |

|       |          | $LCDMX1 LCDMX0 = 00 \implies Static$                |            |

|       |          | $LCDMX1 LCDMX0 = 01 \implies 2-mux$                 |            |

|       |          | LCDMX1 LCDMX0 = 10 $\Rightarrow$ 3-mux              |            |

|       |          | $LCDMX1 LCDMX0 = 11 \implies 4-mux$                 |            |

| 2     | LCDSON   | LCD segments on when LCDSON = $1$ .                 |            |

| 0     | LCDON    | LCD_A module active when LCDON = $1$ .              |            |

# LCDAPCTL1, LCD\_A Port Control Register 1

| 7 |        | 2 | 1      | 0      |

|---|--------|---|--------|--------|

|   | Unused |   | LCDS36 | LCDS32 |

| Bit |        | Description                  |

|-----|--------|------------------------------|

| 1   | LCDS36 | LCD Segment 36 to 39 Enable. |

| 0   | LCDS32 | LCD Segment 32 to 35 Enable. |

# LCDAPCTLO, LCD\_A Port Control Register 0

| 7      | 6      | 5      | 4      | 3      | 2     | 1     | 0     |

|--------|--------|--------|--------|--------|-------|-------|-------|

| LCDS28 | LCDS24 | LCDS20 | LCDS16 | LCDS12 | LCDS8 | LCDS4 | LCDS0 |

| Bit |        | Description                  |

|-----|--------|------------------------------|

| 7   | LCDS28 | LCD Segment 28 to 31 Enable. |

| 6   | LCDS24 | LCD Segment 24 to 27 Enable. |

| 5   | LCDS20 | LCD Segment 20 to 23 Enable. |

| 4   | LCDS16 | LCD Segment 16 to 19 Enable. |

| 3   | LCDS12 | LCD Segment 12 to 15 Enable. |

| 2   | LCDS8  | LCD Segment 8 to 11 Enable.  |

| 1   | LCDS4  | LCD Segment 4 to 7 Enable.   |

| 0   | LCDS0  | LCD Segment 0 to 3 Enable.   |

# LCDAVCTLO, LCD\_A Voltage Control Register 0

| 7      | 6      | 5    | 4       | 3       | 2    | 1    | 0     |

|--------|--------|------|---------|---------|------|------|-------|

| Unused | R03EXT | REXT | VLCDEXT | LCDCPEN | VLCD | REFx | LCD2B |

| Bit   |          | Description                                                                                                                                                                                                                                                       |

|-------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6     | R03EXT   | V5 voltage select:<br>R03EXT = 0 $\Rightarrow$ V5 is AV <sub>SS</sub> .<br>R03EXT = 1 $\Rightarrow$ V5 is sourced from the R03 pin.                                                                                                                               |

| 5     | REXT     | V2 – V4 voltage source selection:<br>REXT = 0 $\Rightarrow$ V2 – V4 are generated internally.<br>REXT = 1 $\Rightarrow$ V2 – V4 are sourced externally                                                                                                            |

| 4     | VLCDEXT  | $ \begin{array}{ll} V_{\text{LCD}} \text{ source select:} \\ VLCDEXT = 0 \Rightarrow \\ VLCDEXT = 1 \Rightarrow \\ \end{array} \begin{array}{ll} V_{\text{LCD}} \text{ is generated internally.} \\ V_{\text{LCD}} \text{ is generated externally.} \end{array} $ |

| 3     | LCDCPEN  | Charge pump enable:<br>LCDCPEN = $0 \Rightarrow$ Charge pump disabled.<br>LCDCPEN = $1 \Rightarrow$ Charge pump enabled when VLCDEXT = 0<br>and VLCDx > 0 or VLCDREFx > 0.                                                                                        |

| 2 - 1 | VLCDREFx | Charge pump reference select:VLCDREF1 VLCDREF0 = $00 \Rightarrow$ Internal.VLCDREF1 VLCDREF0 = $01 \Rightarrow$ External.VLCDREF1 VLCDREF0 = $10 \Rightarrow$ Reserved.VLCDREF1 VLCDREF0 = $11 \Rightarrow$ Reserved.                                             |

| 0     | LCD2B    | Bias select (for any of the mux modes):<br>LCD2B = $0 \Rightarrow 1/3$ bias.<br>LCD2B = $1 \Rightarrow 1/2$ bias.                                                                                                                                                 |

# LCDAVCTL1, LCD\_A Voltage Control Register 1

| 7      | 4 | 3 | 2    | 1 | 0      |

|--------|---|---|------|---|--------|

| Unused |   | V | LCDx |   | Unused |

| Bit   |       | Description                    |               |                     |

|-------|-------|--------------------------------|---------------|---------------------|

| 4 - 1 | VLCDx | Charge pump voltage select:    |               |                     |

|       |       | VLCD3 VLCD2 VLCD1 VLCD0 = 0000 | $\Rightarrow$ | Disable.            |

|       |       | VLCD3 VLCD2 VLCD1 VLCD0 = 0001 | $\Rightarrow$ | $V_{LCD} = 2.60 V.$ |

|       |       | VLCD3 VLCD2 VLCD1 VLCD0 = 0010 | $\Rightarrow$ | $V_{LCD} = 2.66 V.$ |

|       |       | VLCD3 VLCD2 VLCD1 VLCD0 = 0011 | $\Rightarrow$ | $V_{LCD} = 2.72 V.$ |

|       |       | VLCD3 VLCD2 VLCD1 VLCD0 = 0100 | $\Rightarrow$ | $V_{LCD} = 2.78 V.$ |

|       |       | VLCD3 VLCD2 VLCD1 VLCD0 = 0101 | $\Rightarrow$ | $V_{LCD} = 2.84 V.$ |

|       |       | VLCD3 VLCD2 VLCD1 VLCD0 = 0110 | $\Rightarrow$ | $V_{LCD} = 2.90 V.$ |

|       |       | VLCD3 VLCD2 VLCD1 VLCD0 = 0111 | $\Rightarrow$ | $V_{LCD} = 2.96 V.$ |

|       |       | VLCD3 VLCD2 VLCD1 VLCD0 = 1000 | $\Rightarrow$ | $V_{LCD} = 3.02 V.$ |

|       |       | VLCD3 VLCD2 VLCD1 VLCD0 = 1001 | $\Rightarrow$ | $V_{LCD} = 3.08 V.$ |

|       |       | VLCD3 VLCD2 VLCD1 VLCD0 = 1010 | $\Rightarrow$ | $V_{LCD} = 3.14 V.$ |

|       |       | VLCD3 VLCD2 VLCD1 VLCD0 = 1011 | $\Rightarrow$ | $V_{LCD} = 3.20 V.$ |

|       |       | VLCD3 VLCD2 VLCD1 VLCD0 = 1100 | $\Rightarrow$ | $V_{LCD} = 3.26 V.$ |

|       |       | VLCD3 VLCD2 VLCD1 VLCD0 = 1101 | $\Rightarrow$ | $V_{LCD} = 3.32 V.$ |

|       |       | VLCD3 VLCD2 VLCD1 VLCD0 = 1110 | $\Rightarrow$ | $V_{LCD} = 3.38 V.$ |

|       |       | VLCD3 VLCD2 VLCD1 VLCD0 = 1111 | $\Rightarrow$ | $V_{LCD} = 3.44 V.$ |

# 8.5 Laboratory 4: LCD message display

This hands-on laboratory consists of configuring the LCD\_A controller of the MSP430FG4618 device of the Experimenter's board to display a message on the LCD display. As in the case of the previous exercise (Lab3), this laboratory is composed of some sub-tasks. This laboratory has been developed for *Code Composer Essentials version 3* software development tool only.

#### **Project files**

| C source files: | Chapter 8 > Lab4 > Lab4_student.c  |

|-----------------|------------------------------------|

|                 | Chapter 8 > Lab4 > LCD_defs.h      |

| Solution file:  | Chapter 8 > Lab4 > Lab4_solution.c |

### Overview

This laboratory will explore the LCD\_A controller of the MSP430FG4618 device included on the Experimenter's board. This application demonstrates the activation of various LCD segments.

#### A. Resources

The Experimenter's board uses a LCD, which does not have its own controller. The operation is controlled by MSP430FG4618. The interface between these two components is described in the Experimenter's Board datasheet. It is also recommended that the LCD datasheet be read.

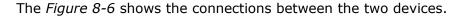

Figure 8-6. Connections between the MSP430FG4618 and the Softbaugh LCD SBLCDA4.

|                                                                                                                                                                         | SoftBaugł                                                                                                                                                                                                               | n SBLCDA4                                                                                                                                                     |                                                                                                                                                                                                                                                                                                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S0 P\$14<br>S1 P\$13<br>S2 P\$12<br>S3 P\$11<br>S4 P\$10<br>S5 P\$9<br>S6 P\$8<br>S7 P\$7<br>S8 P\$6<br>S9 P\$5<br>S10 P\$4<br>S11 P\$3<br>S12 P\$2<br>S1 <u>3 P\$1</u> | 1A_1B_1C_1D<br>1F_1G_1E_DP1<br>2A_2B_2C_2D<br>2F_2G_2E_DP2<br>3A_3B_3C_3D<br>3F_3G_3E_COL3<br>4A_4B_4C_4D<br>4F_4G_4E_DP4<br>5A_5B_5C_5D<br>5F_5G_5E_COL5<br>6A_6B_6C_6D<br>6F_6G_6E_DP6<br>7A_7B_7C_7D<br>7F_7G_7E_DP7 | DOL_ERR_MINUS_MEM<br>ENV_TX_RX_88C<br>ANT_A2_A1_A0<br>BT_B1_80_BB<br>AU_AR_AD_AL<br>PL_P0_P1_P2<br>F1_F2_F3_F4<br>F5_PR_P4_P3<br>COM0<br>COM1<br>COM2<br>COM3 | P\$26         S21           P\$25         S20           P\$24         S19           P\$23         S18           P\$22         S17           P\$21         S16           P\$20         S15           P\$18         COM0           P\$18         COM1           P\$15         COM3           P\$15         COM3 |

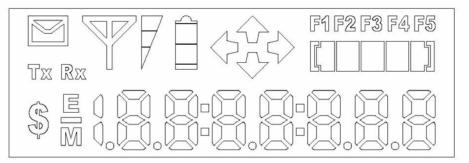

The description of each segment is shown in *Figure 8-7*.

8 6 3 5 Δ 7 2 Г DOL RX D ERR А F В F1 F3 F4 F2 F5 MINUS G F1 F2 F3 F4 F5 С Е D MEM ANT ΒT 4U A2 AR Β1 A1 B0 A0 AD BB P0 PL PR P1 P2 P4 P3 ENV

Figure 8-7. Softbaugh LCD SBLCDA4 segments description.

The information is organized in the LCD as shown in *Figure 8-8*.

# Figure 8-8. Softbaugh LCD SBLCDA4 segments display.

Based on this information, it is possible to define the values to write to each of the memory registers to turn on the desired segments, or to set several of them, as is the case with numbers. The definitions are listed in the Annex to this laboratory.

From analysis of the Experimenter's Board schematics, it can be seen that there is a 10  $\mu F$  between the LCDCAP pin and ground, which means it is possible to use the charge pump.

The segments shared by the I/O function are not used by the LCD, being connected to the segments S4 to S25. The four lines COM0, COM1, COM2, and COM3 are used. The last three lines are shared by ports P5.2, P5.3 and P5.4, respectively. The LCD is operated in 4-mux mode.

The pins R03, R13, R23 and LCDCAP\R33 are used to provide the V5, V4, V3, V2 and V1 (VLCD) voltages, using an external resistor network. They are available at Header H5.

In the current Experimenter's Board configuration, it is possible to select the AVss or charge pump to provide the V1 (VLCD), V2, V3, V4 and V5 voltages. These voltages are only generated when LCD\_A module and the ACLK clock are active. This allows the use of low power mode 3 (LPM3).

Timer\_A, together with the TACCR0 unit are used to generate an interrupt once every second. LED1 and LED2 are switched at each Timer\_A interrupt.

The push button SW1 is used to change the value of voltage generated by the charge pump. The push button SW2 is used to change the LCD frequency.

#### B. Organization of software application

The application starts by configuring the Ports P5.2, P5.3, P5.4 to special function COM1, COM2 and COM3, respectively. The function of COM0 is not shared with the digital I/O functions.

Then, the pins with multiplexed functions are selected to perform the functions necessary to control the LCD segments.

The LCD\_A control register and the voltage configuration register are also configured.

There then follows the execution of the LCD clear routine *LCD\_all\_off()*, which ensures that all segments of the LCD are off.

Timer\_A is configured with its TACCRO unit to generate an interrupt once every second. The ISR generates the memory clock with msec, sec and min, and also connects/disconnects the remaining LCD symbols.

The port pins P2.1 and P2.2 drive LED2 and LED1, respectively. Hence, these ports are configured as digital outputs.

Push buttons SW1 and SW2 have the capacity to generate an interrupt through a change at ports P1.0 and P1.2 respectively. The interrupt ISR, after decoding its source, modifies the LCD operation frequency or modifies the VLCD voltage.

Finally, all the interrupts are activated and the system enters low power mode LPM3.

#### C. System configuration

#### LCD\_A interface with the LCD configuration

Select the function COM1, COM2 and COM3. What is the value to write to these registers?

| P5DIR | = | ; |  |

|-------|---|---|--|

| P5SEL | = | ; |  |

The LCD segments are controlled by the S4 to S25 LCD memory segments. Activate these segments by writing to correct value to the following register:

LCDAPCTL0 = \_\_\_\_;

#### LCD operation frequency

The LCD is to operate in 4-mux mode, with a 30 Hz to 100 Hz refresh frequency. It uses the following equation to determine the LCD operation frequency,  $f_{LCD}$ :

$f_{LCD} = 2 x mux x f_{frame}$

Choose the frequency that provides greatest energy savings.

### □ LCD\_A configuration

The LCD\_A module is to be activated in 4-mux mode from a 32768 Hz clock. What value should be written to the following register?

LCDACTL = \_\_\_\_;

Use the charge pump to internally generate all the voltages necessary for the operation of the LCD, using a bias 1/3. What is the value to write to the register?

LCDAVCTLO = \_\_\_\_;

The charge pump generates a LCD voltage of 3.44 volts. Configure the following register:

LCDAVCTL1 = \_\_\_\_;

#### □ Timer\_A configuration

The Timer\_A generates an interrupt once every second. It uses the TACCR0 unit. Configure the following registers:

TACCTL0 = \_\_\_\_\_; TACCR0 = \_\_\_\_\_; TACTL = \_\_\_\_\_;

#### Output ports configuration

Configure the ports connected to LED1 and LED2 in order to make one of them active and the other inactive at system start up:

P2DIR |= \_\_\_\_\_; P2OUT |= \_\_\_\_\_;

#### Input ports configuration

The push buttons SW1 and SW2 generate an interrupt on a low-tohigh transition. Configure the necessary registers:

| P1DIR  = | _; |

|----------|----|

| PIIES =  | ;  |

| P1IE  =  | ;  |

#### D. Operation analysis

Compile the project, load it into microcontroller's memory and execute the application. For each value of the operating frequency and voltage generated by the charge pump, measure the electrical current consumption. Draw a graph of these results and draw conclusions concerning the energy consumption.

#### MSP-EXP430FG4618

#### SOLUTION

Configure the LCD\_A controller of the MSP430FG4618 device of the Experimenter's board to display a message on the display.

□ LCD\_A interface with the LCD configuration:

#### □ LCD operation frequency:

```

LCDACTL = LCDFREQ_192 | LCD4MUX; // (ACLK = 32768)/192

// and 4-mux LCD

```

#### □ LCD\_A configuration:

| LCDACTL  = LCDSON   LCDON; | // LCD_A on and Segments on |

|----------------------------|-----------------------------|

| LCDAVCTL0 = LCDCPEN;       | // Charge pump enable       |

| LCDAVCTL1 = VLCD_3_44;     | // VLCD = 3.44 V            |

#### □ Timer\_A configuration:

TACCTL0 = CCIE; // TACCR0 interrupt enabled TACCR0 = 3268; // this count correspond to 1 msec TACTL = TASSEL\_1 + MC\_1 + ID\_0; // ACLK, up mode Output ports configuration:

| P2DIR $\mid = 0 \times 06;$ | // P2.1 and P2.2 as output |

|-----------------------------|----------------------------|

| P2OUT  = 0x04;              | // LED2 off and LED1 on    |

#### □ Input ports configuration:

| P1DIR &= ~0x03; | // P1.0 and P1.1 digital inputs      |

|-----------------|--------------------------------------|

| P1IES  = 0x03;  | // low-to-high transition interrupts |

| PIIE $ = 0x03;$ | // enable port interrupts            |

# 8.6 Quiz

**1.** The fractional LCD biasing voltages V2, corresponds to which fraction of full-scale voltage?

- (a) 1/1;

- (b) 1/2;

- (c) 2/3;

- (d) 1/3.

**2**. To blink the LCD, the following LCD\_A control register bit must be set:

- (a) LCDON;

- (b) LCDSON;

- (c) LCDCPEN;

- (d) LCD2B.

3. To source the fractional LCD biasing voltages externally:

- (a) Reset OSCOFF and LCDON bits;

- (b) Set OSCOFF bit;

- (c) Reset LCDON bit;

- (d) Set OSCOFF and LCDON bit.

4. To configure a LCD period of approximately 10 milliseconds:

- (a) LCDMXx = 1;

- (b) LCD2B = 1;

- (c) LCDFREQx = 3;

- (d) LCDFREQx = 7.

- 5. An LCD with 3-mux, 1/3 bias configuration requires:

- (a) LCDMXx = 2 and COM = 3;

- (b) LCD2B = 0;

- (c) All of the above;

- (d) None of the above.

- 6. An LCD with 3-mux, 1/2 bias has the capacity to drive:

- (a) 90 segments;

- (b) 160 segments;

- (c) 140 segments;

- (d) 64 segments.

**Solution:** 1, (c); 2, (b); 3, (a); 4, (d); 5, (c); 6, (a)

## 8.7 FAQs

**1**. What is the maximum number of segment lines controllable using the LCD\_A controller?

The maximum number of segment lines available differs between devices. See the device-specific datasheet for details.

2. LCDSx Bits affect dedicated LCD segment pins?

No. The LCDSx bits only affect pins with multiplexed LCD segment functions and digital I/O functions.

3. What should be the capacitor value for the internal charge pump?

It is recommended that a 4.7  $\mu\text{F}$  capacitor or larger is connected between the LCDCAP pin and ground.