## EVikings II

# Establishment of the Virtual Centre of Excellence for IST RTD in Estonia

IST-2001-37592 WP 4

Deliverable D4.7c

## **Final Report**

## WP4 (November 2002- September 2005)

R.Ubar

Tallinn University of Technology Department of Computer Engineering

2005

## CONTENTS

| 1. Introduction                                                 | 3 |

|-----------------------------------------------------------------|---|

| 2. Main results                                                 | 5 |

| - Decision diagrams for diagnostic modeling of digital systems  |   |

| - Fault modeling and a new uniform fault model                  |   |

| - A new defect-oriented deterministic test generator            |   |

| - Hierarchical automated test generation with decision diagrams |   |

| - Hybrid built-in self-test in Systems-on-Chip                  |   |

| - Network-on-Chip interconnect testing                          |   |

| - Fault simulation accelerator based on reconfigurable hardware |   |

| - Design for testability                                        |   |

| - Creating a multifunctional research environment               |   |

| - E-learning environment for Web-based study of testing         |   |

| 3. Cooperation with industry                                    | 6 |

| 4. Academic international cooperation                           | 8 |

| 5. Dissemination of results                                     | 3 |

| 6. Self-evaluation of the project results                       | 6 |

| 7. Full description of each delieverable                        | 8 |

| 8. Future perspectives                                          | 5 |

| 9. Final conclusions 4'                                         | 7 |

| 10. Publications 49                                             | 9 |

## **1. INTRODUCTION**

Electronic systems are becoming ubiquitous and their reliability issues are present in all types of consumer applications. In order to guarantee a high level of reliability, adequate testing of electronic products is required. However, testing contemporary electronic systems is an extremely hard task. Furthermore, the ever-increasing complexity of these systems causes the need for new, more efficient test methods.

The general aim of the work package was to strengthen and support research and development activities in line with the MEDEA roadmap in design and test of digital systems, and implementation of new research results as innovative new CAD tools in the local industry. The goal was also to strengthen international research contacts via mutual co-operation with European research institutions.

The research in this workpackage was carried out in a broad field of digital design and test. The following topics were covered: design for testability, fault modeling and fault analysis, reconfigurable hardware based accelerators for fault simulation, test generation, design of self-testing systems. A lot of useful results have been achieved and published in a recognized journals and proceedings. Continuous experimental work has been carried that was needed for proving the efficiency of new algorithms and methods. As a result, a lot of prototype tools were created and combined in a multi-functional CAD environment that has been used both for research and teaching purposes. This environment was and is being used for several projects with Estonian industry. New testing methodologies were developed and experimented in cooperation with company Artec Design. Novel BIST ideas are being developed and used for industrial purposes in a Technology Development Centre ELIKO: a new national centre uniting Estonian microelectronics SMEs and Tallinn University of Technology to carry out applied and basic research projects. New Boundary Scan and interconnect testing methods developed in the project will be now the content of the new industrial projects to be contracted with Testonica Lab in Estonia and with Ericsson AB and SAAB in Sweden.

The new quality and originality of the environment developed in the project is in the property of multi-functionality of the system (important for research and training), low-cost and ease of use. The multi-functionality means that different abstraction level models can be easily synthesized and resynthesized (to analize the influence of the complexity of the model to the efficiency of methods), the methods are implemented by different algorithms (to analize the efficiency of different approaches), the fault models can be easily changed and updated (to analyze the adequacy and accuracy of testing). The multi-functionality allows to set up and modify easily different experimental schemes and scenarios for investigating new ideas and methods. It gives an excellent opportunity for students to understand the ideas, advantages and drawbacks of different methods at changeable conditions. In traditional commercial design tools these purely research oriented possibilities are missing. On the other hand, in many cases the commercial tools can be replaced by new tools developed in WP4 in small design companies also for commercial design purposes, because of their low-cost and ease of

use compared to the very expensive commercial systems.

Based on this environment intensive international cooperation has been carried out which has resulted in a lot of joint research results and publications with international partners from more than 10 countries. 6 international conferences and workshops were organized in WP3 during the project years instead of only three that were initially planned. We had all together 14 student placements at international partner institutions, and 3 placements in the industry. This helped to strengthen the cooperation with industry and with international academic world. As the result we published during the last 3 years all together 50 joint papers with foreign co-authors where the initiative belonged mostly to our researchers, and where the main experimental research was carried out in the environment created as the result of the project.

Thanks to the project, an intensive cooperation has been started with several academic and research institutions in Estonia, like Tartu University (2 joint papers, a placement of a PhD student at TU Tallinn, joint seminars in Tartu and Tallinn), Institute of Cybernetics (joint tasks in the projects of ELIKO) etc.

The cooperation between other WPs of the project was targeted to organization of joint courses and seminars. For example, at Computer Theory Days organized by Institute of Cybernetics (WP2), October 3-5, 2003, DCE lecturers (involved in WP4) held a full session on digital microelectronics design: Prof. P. Ellervee "High-level synthesis and hardware compilation", Prof. K. Tammemae "Co-design: from practice to theory. There are joint projects of people involved in WP2 and WP3 that are coordinated by the development centre ELIKO which itself can be regarded as a "product of the current project".

The project helped considerably to strengthen the level of teaching design and test topics in the curricula at TTU. A full cycle of digital design and test courses were developed in WP4. The created E-learning environment for Web-based study of design and test allowed to make teaching more attractive and efficient. It also allowed to engage better MSc and PhD students in the research activities of the group which is very important for maintaining the momentum of future research in the current field of designing and testing of SoC and NoC.

## 2. MAIN RESEARCH RESULTS

The increasing complexity of electronic systems has made testing one of the most complicated and time-consuming problems in system design and production. The rapid developments in the areas of deep-submicron electron technology and design automation tools are enabling engineers to design larger and more complex electronic systems. According to the Moore's law, the computer power doubles roughly every 18 months. This means that since 1950 the computer power has increased by a factor of about 10 billions. This increase is larger than the transition from chemical explosives to the hydrogen bomb.

The more complex are electronic systems getting the more probable will be the failures, and the more important will be the problems of testing. Nanometer technologies introduce new formidable challenges making test quality a very fast moving target. The importance of test and design for testability is growing because the expenses of verification and test are becoming the major components of the design and manufacturing costs of new products.

The main problems in the test field are related to the continuously growing complexity of systems which make testing and fault diagnosis extremely difficult. New hierarchical approaches are needed to cope with the growing complexity and the testing quality needs.

Several novel conceptions were introduced, developed and investigated in the project:

- uniform approach to hierarchical diagnostic modeling of digital systems based on using decision diagrams;

- new conception of mapping faults from one hierarchical level to another based on a novel functional fault model;

- a conception of hybrid self-testing architectures where slow but exact deterministic testing methods are optimally combined with fast and not exact on-line testing methods;

- combining of reconfigurable hardware and software to increase the efficiency of traditionally by software solved algorithmic solutions in the design and test field.

Based on these novel conceptions, the main research activities that took place in WP4 can be split into the following different topics:

- Decision diagrams for diagnostic modeling of digital systems

- Fault modeling and a new uniform fault model

- A new defect oriented deterministic test generator

- Hierarchical automated test generation with decision diagrams

- Hybrid built-in self-test in Systems-on-Chip

- Network-on Chip interconnect testing

- Fault simulation accelerator based on reconfigurable hardware

- Design for testability

- Creating a multifunctional research environment

- E-learning environment for Web-based study of testing

A short overview of the content of research and the achieved results in the listed topic areas will follow. The references are to the publications produced in the frame of the project during the years 2003-2005.

## 2.1. Decision Diagrams for Diagnostic Modeling of Digital Systems

Hierarchical approach was the main methodology we used in solving the test problems for complex digital systems. As the mathematical basis we used a new original diagnostic model for digital systems – Decision Diagrams (DD), developed by the group. The well known Binary Decision Diagrams (BDD) can be considered as a particular case of this model. DD-s allowed us to investigate and solve the problems of test synthesis and analysis uniformly at different abstraction levels of digital systems.

For logic level diagnostic modeling we developed a special class of BDDs – structurally synthesized BDDs (SSBDD) to represent the topology of gate-level circuits in terms of signal paths. Unlike "traditional" BDDs, SSBDDs directly support test generation for gate-level structural faults without representing these faults explicitly. The advantage of the SSBDD based approach is that the library of components is not needed for structural path activization. This is the reason why SSBDD based test generation procedures do not depend on whether the circuit is represented on the gate level or on the macro-level whereas the macro means an arbitrary single-output subcircuit of the whole circuit. This independence makes SSBDDs extremely efficient for hierarchical logic level test generation. Several new interesting features were discovered in the SSBDD model which allowed to increase the simulation speed on SSBDDS [3,4,61,67].

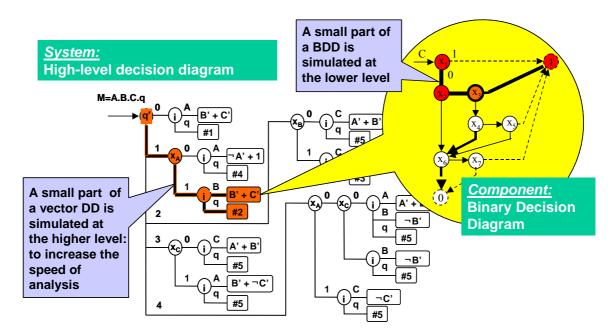

Figure 1. Hierarchical modeling with DDs

The drawback of traditional multi-level and hierarchical approaches to digital test lies in the need of different dedicated languages and models for different levels. Using DDs we were able to develop uniform methods for hierarchical diagnostic modeling of digital systems.

It came out that the methods developed for Binary DDs were suitable for generalization for using them also for higher level DDs [9,44,84]. Several methods were developed to compress the high-level DD-model to further increase the simulation speed. Examples are complex DDs where a group of simple high-level DDs representing several high-level components are joined into a single vector DD. In vector DDs the parts of different high-level components can be simulated in parallel.

In Figure 1 the idea of hierarchical diagnostic modeling is illustrated. A small part of a vector DD is simulated. When an error is detected, and located to the high level component (adder) B+C, then the adder can be represented more exactly at the lower logic level for exact fault location in the logic circuits with accuracy of signal lines or gate-level components.

#### New results:

- 1. Recent research showed that generalization of BDDs for higher levels provides a uniform fault model for both gate and RT level or even behavioral level fault modeling, fault simulation and test generation [54, 80].

- 2. Based on SSBDDs and high level DDs new efficient hierarchical methods for logic level fault simulation [2,12,93] and test generation [18], hierarchical fault simulation [65,86] and test generation [21,55,69,102] were developed.

### 2.2. Fault Modeling and a New Uniform Fault Model

As the complexity of digital systems continues to increase, the traditional low level diagnostic analysis methods have become obsolete. Other approaches based mainly on higher level functional and behavioral methods are gaining more popularity.

However, the trend towards higher level modeling moves us even more away from the real life of defects and, hence, from accuracy of testing. To handle adequately defects in deep-submicron technologies, new fault models and defect-oriented test methods should be used. On the other hand, the defect-orientation is increasing even more the complexity.

To get out from the deadlock, the two opposite trends – high-level modeling and defectorientation – should be combined into hierarchical approaches. The advantage of hierarchical approaches compared to high-level functional modeling lies in the possibility of constructing test plans on higher levels, and modeling faults on more detailed lower levels.

Consider a Boolean function  $y = f(x_1, x_2, ..., x_n)$  of a component (library cell) C in a circuit. Introduce a Boolean variable *d* for representing a given physical defect in the component, which converts *f* into another faulty function  $y = f^d(x_1, x_2, ..., x_n)$ . Introduce for C a generic function

$$y^* = f^*(x_1, x_2, ..., x_n d) = \overline{d} f \lor df^d$$

(1)

which describes the behavior of the component simultaneously for both fault-free and faulty cases. The solutions of the equation

$$W^{d} = \frac{\partial y^{*}}{\partial d} = 1 \tag{2}$$

describe the conditions which activate the defect *d* to a line *y*. The conditions  $W^d$  allow to map physical defects *d* to logic level. The constraint  $W^d = 1$  defines how a lower level fault *d* should be activated at a higher level to a given node *y*.

A pair  $(W^d, y)$  was defined as a uniform abstract functional fault model for a physical defect or for a group of physical defects, free from any details of the real defects it is representing [16,18 (best paper award)].

On the other hand, this model can be regarded as an interface for mapping faults from one system level to another, helping to carry out hierarchical test generation.

In the described approach we have to characterize all possible defects in all library cells, and represent the results as defect tables. The defect characterization may be computationally expensive, but it is performed only once for every library cell.

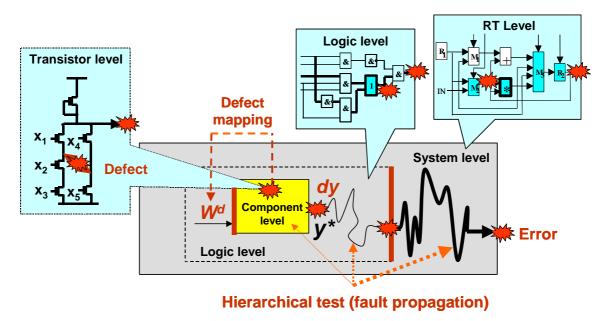

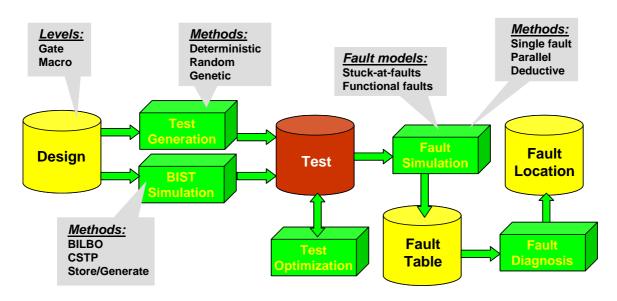

#### Figure 2. Hierarchical test generation and fault simulation

In Figure 2, an example of a hierarchical fault activation and propagation for test generation purposes is illustrated. A physical defect in a component (library cell) at a low transistor or layout level is mapped as a logic condition  $W^d = 1$  to the logic level and the result of mapping as a functional fault  $(W^d, y)$  is stored in the cell library. The erroneous signal dy on a line y is propagated on the logic level to an output of the corresponding logic level module, and thereafter on the higher level (register transfer or instruction set level) from this point to an observable point (to primary output or to memory for storing) for observing as an erroneous signal.

New results:

- 1. The new functional fault model allows to handle arbitrary physical defects by purely logic methods and algorithms [80,92].

- 2. The model creates a simple conception and basis for hierarchical test generation and fault simulation [90].

## 2.3. A New Defect-Oriented Deterministic Test Pattern Generator

A method was developed for deterministic test pattern generation using a uniform functional fault model for combinational circuits. The fault model allows to represent arbitrary physical defects in components and defects in the communication network of components by the same technique. Physical defects in components are modeled as parameters in generic Boolean differential equations. Solutions of these equations give the conditions  $W^d = 1$  for activating defects locally. The possibility of detecting the bridging faults that via feedback will

transform a combinational circuit into a sequential one is also created. A method is proposed which allows to find the types of faults that may occur in a real circuit and to determine their probabilities.

A defect-oriented deterministic test generation tool was developed (DOT), and the experimental data obtained by the tool for benchmark circuits are presented in Table 1. It was shown that 100% stuck-at fault tests covered only about 75-82% physical defects (column 5 in Table 1). The main feature of the new tool is its ability to reach 100% defect testing efficiency (percentage of covering the nonredundant defects) for the given set of defects by proving the redundancy of not detected defects. The tool allows to prove the redundancy of physical defects in relation to the logic behaviour of a circuit. Such a function of the tool to prove the redundancy of physical defects to our knowledge in unique in the world.

Column 6 in the Table 1 shows the defect testing efficiency after proving the redundancy of defects inside the library cells, and column 7 shows the defect testing efficiency after proving the redundancy for the whole set of defects. The column 8 shows the defect testing efficiency reached by the test generation tool DOT.

|         | Nu      | mber of de | fects      | Defect coverage          |       |        |        |  |

|---------|---------|------------|------------|--------------------------|-------|--------|--------|--|

| Circuit | All     | Redunda    | nt defects | 100% stuck-at fault ATPG |       |        | DOT    |  |

|         | defects | Gates      | System     |                          |       |        |        |  |

| 1       | 2       | 3          | 4          | 5                        | 6     | 7      | 8      |  |

| c432    | 1519    | 226        | 0          | 78,6                     | 99,05 | 99,05  | 100,00 |  |

| c880    | 3380    | 499        | 5          | 75,0                     | 99,50 | 99,66  | 100,00 |  |

| c2670   | 6090    | 703        | 61         | 79,1                     | 98,29 | 98,29  | 100,00 |  |

| c3540   | 7660    | 985        | 74         | 80,1                     | 98,52 | 99,76  | 99,97  |  |

| c5315   | 14794   | 1546       | 260        | 82,4                     | 97,73 | 99,93  | 100,00 |  |

| c6288   | 24433   | 4005       | 41         | 77,0                     | 99,81 | 100,00 | 100,00 |  |

This work on defect-oriented testing has been carried out in a cooperation between TU Darmstadt (Germany), University of Technology in Warsaw (Poland) and TU Tallinn.

The main results of this research are published in the papers [27,37,38].

New results:

- 1. The first time a tool was created for proving redundancy of physical defects. This feature of the tool allows to evaluate the quality of test generation more adequately than the existing tools can do [27,37,38].

- 2. The new tool allows to reach 100% defect coverage, that other existing tools cannot do because they miss the accurate measure [17,73,79].

- 3. The model creates a simple conception and basis for hierarchical test generation and fault simulation [90].

## 2.4. Automated Test Pattern Generation with Hierarchical DDs

The following research was carried out in the field of hierarchical test pattern generation. New fault models for multiplexers in hierarchical designs were developed. The new models covered 100 % of stuck-at faults in multiplexers embedded to datapaths. Additional important

result was development of fault models to target conditional operators in digital systems [54]. Both fault models were implemented and tested on a hierarchical test pattern generation tool DECIDER<sup>1</sup> created at Tallinn University of Technology. The experiments showed significant improvement in comparison to state-of-the-art test generation approaches.

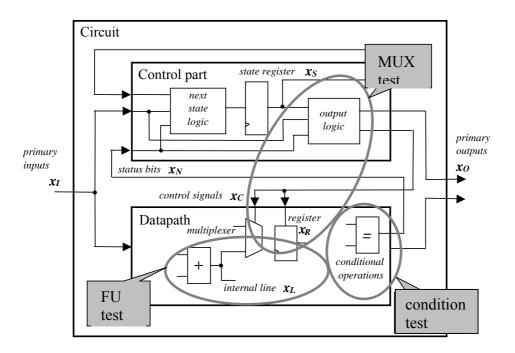

In the following, we will explain the fault models implemented in current approach, where a combination of three fault models is used. These include a hierarchical fault model for Functional Units (FU), a functional model for multiplexers [55] and a combined hierarchical-functional model for conditional operations [254. Circuit areas targeted by each of the above models are marked in Fig. 1 by grey circles.

#### 2.4.1. New functional fault models for multiplexers

Makar and McCluskey<sup>2</sup> presented the groundwork for deriving minimal tests for AND/OR, OR/AND and nMOS implementations of multiplexers. The functional fault model developed in the framework of e-Vikings II project is similar but it extends it with the ability to cover multiple stuck-at faults at the address select inputs of the MUX under test. This, in turn, provides for potentially better coverage of faults in the output logic of the control part FSM.

The new functional model is based on distinguishing values at the data inputs of the MUX. For multiplexers having more than two data inputs we have chosen to implement pair-wise distinguishing of data inputs as opposed to distinguishing all the inputs simultaneously. The main motivation for that is that high-level path justification from all inputs may be difficult to achieve. Moreover, it can lead to inconsistencies and therefore to loss of solutions.

Figure 3. Coverage of new hierarchical fault models

<sup>&</sup>lt;sup>1</sup> J.Raik, R.Ubar. Fast Test Pattern Generation for Sequential Circuits Using Decision Diagram Representations. *Journal of Electronic Testing: Theory and Applications*, Kluwer Academic Publishers. Vol. 16, No. 3, pp. 213-226, June, 2000.

<sup>&</sup>lt;sup>2</sup> Makar, S.R., and E.J. McCluskey, "On The Testing Of Multiplexers," Proc. 1988 Int. Test Conf., Washington, DC, pp. 669-679, September 12-14, 1988.

Note, that treating MUXs by a hierarchical fault model similar to the one used for FUs would not have allowed targeting faults in the control part. Furthermore, a slow, three-valued fault simulator would have been needed for evaluating the fault coverage achieved in the multiplexers at the low level. In current work, only AND/OR multiplexers are considered but functional models for other multiplexer types can be derived in a similar way. (e.g. the fault model for OR/AND multiplexers is dual to AND/OR<sup>3</sup>).

#### 2.4.2. Fault model for targeting conditional FUs

The main novel contribution of the project is the new fault model for targeting conditional operations in RTL designs [54]. By conditional operations we mean FUs, whose outputs are used as status bits (or flags) entering the FSM. Here, usually comparison functions are implemented but also outputs of arithmetic and logic functions can be connected to status bits. The main difficulty in testing such modules lies in the fact that no propagation path to primary outputs through the datapath exists for them.

A combined functional hierarchical fault model is used for testing the conditional operations. A functional approach is selected to activate the fault effect at the output of the module under test. Additionally, a hierarchical model [13] is implemented to test the module at the low level. The experimental results showing the improvement provided by the new fault models are presented below.

#### 2.4.3. Experimental results

In Table 2, comparison of test generation results of four ATPG tools are presented on six hierarchical benchmarks. The other tools considered in the comparative experiments include HITEC<sup>4</sup>, which is a logic-level deterministic ATPG, GATEST<sup>5</sup> as a genetic-algorithm based tool and a hierarchical ATPG DECIDER<sup>6</sup>. The column 'current approach' shows the results obtained by the functional-hierarchical method developed in e-Vikings II project.

| circuit       | faults | HITEC <sup>4</sup> |         | GATEST <sup>5</sup> |         | DECIDER <sup>6</sup> |         | current approach |         |

|---------------|--------|--------------------|---------|---------------------|---------|----------------------|---------|------------------|---------|

|               |        | F.C., %            | time, s | F.C., %             | time, s | F.C., %              | time, s | F.C., %          | time, s |

| gcd           | 454    | 81.1               | 169.5   | 91.0                | 75      | 89.9                 | 13.5    | 89.9             | 129.8   |

| sosq          | 1938   | 77.3               | 728.4   | 79.9                | 739     | 80.0                 | 79.3    | 80.1             | 129.6   |

| mult8x8       | 2036   | 65.9               | 1243    | 69.2                | 821.6   | 74.1                 | 50.2    | 74.7             | 93.7    |

| ellipf        | 5388   | 87.9               | 2090    | 94.7                | 6229    | 95.04                | 1197.8  | 95.04            | 1258.9  |

| risc          | 6434   | 52.8               | 49,020  | 96.0                | 2459    | 95.8                 | 85      | 96.5             | 150.5   |

| diffeq        | 10,008 | 96.2               | 13,320  | 96.40               | 3000    | 96.51                | 295.5   | 97.09            | 453.7   |

| average F.C.: |        | 76.9               |         | 87.9                |         | 88.6                 |         | 88.9             |         |

Table 2. Comparison of sequential circuit test generation tools

<sup>3</sup> Makar, S.R., and E.J. McCluskey, "On The Testing Of Multiplexers," Proc. 1988 Int. Test Conf., Washington, DC, pp. 669-679, September 12-14, 1988.

<sup>4</sup> T. M. Niermann, J. H. Patel, "HITEC: A test generation package for sequential circuits", Proc. European Conf. Design Automation (EDAC), pp.214-218, 1991.

<sup>5</sup> E. M. Rudnick, J. H. Patel, G. S. Greenstein, T. M. Niermann, "Sequential Circuit Test Generation in a Genetic Algorithm framework," Proc. DAC., pp. 698-704, 1994.

<sup>6</sup> J.Raik, R.Ubar. Fast Test Pattern Generation for Sequential Circuits Using Decision Diagram Representations. *Journal of Electronic Testing: Theory and Applications*, Kluwer Academic Publishers. Vol. 16, No. 3, pp. 213-226, June, 2000.

The experiments were run on a 366 MHz SUN UltraSPARC 60 server with 512 MB RAM under SOLARIS 2.8 operating system. Actual stuck-at fault coverages of the test patterns generated by all the tools were measured by the same fault simulation software. The test generation times for the proposed method include both, test generation time and evaluation of the gate-level stuck-at fault coverage by the fault simulator.

In Table 2, fault coverages and run times in seconds for each example circuit are presented. The average fault coverage achieved by each tool is reported in the last row. Experiments show that the proposed method reaches the best fault coverage for five out of six examples. At the same time the run times of the hierarchical-functional approach are generally shorter than that of the simulation-based method GATEST and the deterministic ATPG HITEC. While the hierarchical approach published in [3] is slightly faster, its fault coverage in the case of three examples remains lower in respect to the proposed approach. Moreover, increasing the time-out for method [3] did not improve the results.

<u>New results:</u>

- 1. New fault models for multiplexers in hierarchical designs were developed [54,55].

- 2. The ATPG tool developed for using the new fault models reaches the best fault coverage compared to the known university tools whereas commercial hierarchical ATPG tools are missing [13,69,54,55].

## 2.5. Hybrid Built-In Self-Test in Systems-on-Chip

Due to the requirements for the Automatic Test Equipment (ATE) speed and memory, the ATE-based test solution may not always be affordable in terms of cost and accuracy. Therefore, in order to apply at-speed tests and to keep the test costs under control, on-chip, built-in self-test (BIST) solutions are becoming a mainstream technology for testing complex electronic systems.

Different test scenarios are possible, while using BIST. Sometimes the embedded cores may be tested using only internally generated pseudorandom test patterns. Due to several reasons, like very long test sequences, and random pattern resistant faults, this approach may not always be efficient.

One solution to this problem is to complement pseudorandom test patterns with deterministic test patterns, applied from the on-chip memory or, in special situations, from the ATE. This approach is usually referred to as hybrid BIST. One of the important parameters influencing the efficiency of a hybrid BIST approach is the ratio of pseudorandom and deterministic test patterns in the final test set. As the amount of resources on the chip is limited, the final test set has to be designed in such a way that the deterministic patterns fit into the on-chip memory. At the same time the testing time must be minimized in order to reduce testing cost and time-to-market.

Close cooperation in between Tallinn University of Technology and Linköping University, Sweden has given several original results in the area of hybrid BIST. The results have been reported in many high-quality conferences, like DFT, ATS, ETS, in 2 book chapters (published by Springer) and summarized in a monograph "Hybrid Built-In Self-Test and Test Generation Techniques for Digital Systems" (238 pages).

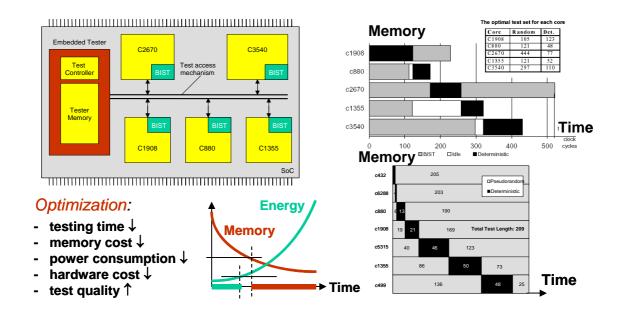

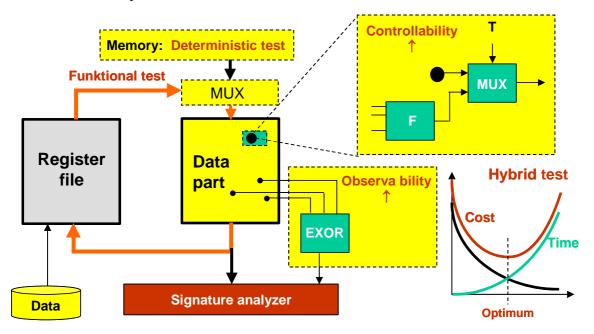

Figure 4. Optimization of hybrid built-in self-test

The main results have been so far a set of novel test cost minimization algorithms (minimization of testing time, memory cost, energy or power consumption, hardware cost) at the demanded test quality and at different design constraints.

We have developed algorithms and methods for test cost calculation together with global hybrid BIST optimization for single-core designs, and under memory constraints for multi-core systems. The methodology is based on a novel idea of cost estimation which allowed developing a fast iterative algorithm to minimize the total length of the hybrid BIST under given memory constraints. In addition we have developed a method for power-constrained system-on-chip test scheduling in an abort-on-first-fail environment where the test is terminated as soon as a fault is detected and proposed a technique to find the best ratio of pseudorandom and deterministic test sequences so that the total energy is minimized and the memory requirements for the deterministic test set are met without sacrificing test quality.

In Figure 4 a multi-core System-on-Chip is presented where all the cores have individual pseudorandom test generators which can work in parallel. A central test controller is coordinating the whole test process and his task is also to apply deterministic test sequences stored in the central memory to all the cores sequentially. The grey parts of test processes on the diagrams on the right show pseudorandom sequences, and the black parts show deterministic sequences. The upper diagram shows a randomly composed test process, the lower diagram shows the optimized one.

We have developed a novel hybrid functional BIST (HyBIST) scheme to combine the functional routines (working routines) carried out in digital systems with additional stored deterministic test patterns for testing microprogrammed data-paths in digital systems [58.68]. In the first test phase (see Figure 5) only the functional resources of a system (register file and data part) are used for testing purposes. A functional microprogram is carried out to control the data-path based on some deterministic input data. A response compressor like signature analyzer is connected to the data path to monitor the process. To quarantee a high test coverage for BIST, the second phase of the test is used which consists of applying additional deterministic test patterns pregenerated by an ATPG to test the random-pattern-resistant faults. Another option could be to improve the controllability and observability of the data part regarding the particular functional test.

A method is proposed to find the tradeoff between the functional test and deterministic test parts. Experimental research demonstrated the feasibility of the approach, and showed the advantage of combining functional and deterministic test patterns compared to the pure deterministic test or pure functional test.

Figure 5. Hybrid functional built-in self-test

#### <u>New results:</u>

- 1. A novel method for fast cost estimation for variations of test processes with complex structure [35,50,77].

- 2. Based of the fast cost estimation method, very efficient iterative methods were developed for optimizing hybrid sequential and parallel test processes at different constraints [5,26,52,60,95-97].

- 3. A conception and implementation of functional BIST was proposed that allows to reduce considerably the hardware cost compared to the traditional BIST methods [58,68].

## 2.6. Network-on-Chip Interconnect Testing

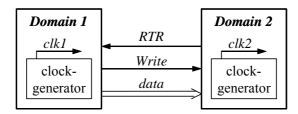

The advances in semiconductor technology will soon allow us to build systems on chips (SoCs) with billions of transistors running at gigahertz frequencies. The bus-based interconnect paradigm widely spread in the board-level systems, lose its prevalence in the SoC world due to extremely high communication complexities of the modern multi-core systems. For the sake of robustness, flexibility, and scalability the bus-based interconnect architecture is being substituted by a packet-switching communication paradigm borrowed from data and computer networking. This new paradigm called Network on Chip (NoC) will be likely to use Globally Asynchronous Locally Synchronous (GALS) approach in order to avoid clock distribution problems in future chips. In GALS designs, a system is partitioned into multiple domains, each having a different clock.

Testing of NoC involves testing of the infrastructure's functional elements (routers/switches)

and conductive interconnect lines. This research concentrates on interconnect testing, which becomes an extremely important challenge due to the gigahertz operating frequencies and small gaps in the wires of high density chips. In such conditions, the crosstalk among interconnections is becoming a critical issue. Because of small dimensions, variations in the fabrication process are also affecting signal integrity and delays. The results of the current research can be classified by two directions: 1) solving the test application and fault detection problem in GALS structures and 2) design of a reconfigurable embedded test generation solution that supports a tradeoff between test speed and test quality and is designed for multi-layer on-chip interconnect structures. Both methods primarily target delay faults and harmful interference due to crosstalk.

Fig.6. Connections in a handshaking protocol.

Fig.7. Data transfer through handshaking

In NoC based architectures, unidirectional physical channels are preferred between two resources or routers for communication, which, accordingly to the GALS paradigm, is asynchronous and uses handshaking signals (Fig.6 and 7). In such paradigm, signals *Write*, *RTR* (Ready-To-Receive) and *Data* are synchronized to the clocks in respective domains. The receiver asserts RTR=1 when it is able to receive new data. The transmitter sends the *Write* signal, which is followed by data transmission.

Fig.8. Signals at the receiver when data is delayed

Because there is no synchronisation between the clocks in the transmitter and receiver, the new data as well as *Write* can arrive in any part of the clock cycle of the receiver. The effect of this is a non-deterministic time gap between arrival of *Write* and reading of data in the receiver. Let  $T_R$  be the clock period of the receiver. Then the time gap between *Write* arrives till the data is actually read is in the interval  $[0, T_R]$  with uniformly distributed probability. Therefore, the data may be received sometimes correctly and sometimes erroneously when a delay fault exists in the data lines (Fig. 8a,b).

Let  $t_l$  be the time from the data arrives till the signal *Write* arrives at the receiver. The probability density function of  $t_l$  is expected to follow the distribution shown in Fig. 9. If  $t_l$  is positive (interval 3 in Fig. 9) there is no delay fault that causes erroneous data. If  $t_l$  has a lower value than  $-T_R$ , (interval 1 in Fig. 9) it means that a delay fault is present that always makes data erroneous. If  $t_l$  is between  $-T_R$  and 0 (interval 2 in Fig. 9) the transferred data are received sometimes erroneously and sometimes correctly.

The basic idea of the proposed conservative test application method is to read the data one clock cycle before it is read under normal operation. Then the test consists of the transmitter sending data many times (say *m* times) with a long or random time gap between two data transfers. It can be shown that if the expected data is received correctly even once in *m* trials then the link is delay fault free. After *m* tests, the chip is marked MIGHT\_BE\_FAULTY, if for all tests the received signal was faulty. It is shown that the probability of declaring a good chip as faulty decreases exponentially with increase in *m*, which is illustrated by Table 3. Therefore, there is a very little chance to mistakenly classify a good link as faulty.

| $t_l/T_R$ | 10 % | 1 % | 0.1 % | 0.01 % |

|-----------|------|-----|-------|--------|

| ≥1        | 1    | 1   | 1     | 1      |

| 0.99      | 1    | 1   | 2     | 2      |

| 0.9       | 1    | 2   | 3     | 4      |

| 0.5       | 4    | 7   | 10    | 14     |

| 0.1       | 22   | 44  | 66    | 88     |

Table 3. Probabilities of declaring a good chip as faulty

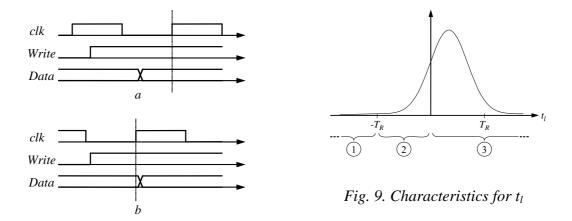

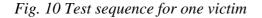

Since, each data line can have two delay faults; one when it changes from 0 to 1 and the other when it changes from 1 to 0, then both transitions have to be tested. In fact, the signal dependency and fault detection conditions are rather more complicated in case of crosstalk. A special conservative but very effective fault model, called Maximum Aggressor fault model was proposed in literature for crosstalk testing. The model divides the link wires into two groups: one is victim and all others are aggressors with respect to the victim. Fig. 10 illustrates this principle. In the table, *i*-th signal is the victim and the patterns represent a complete crosstalk test set (6 patterns) for one victim.

### Fig. 11 Simple test generation HW

Since this fault model is conservative and therefore pessimistic in many cases, it is possible to relax it by allowing more than one victim to be simultaneously present in the link under test.

The test generation (TG) hardware illustrated in Fig. 11 allows for TG scheme to be reconfigured in the range from the most conservative and slow one to more relaxed but much faster one. This brings a freedom of test generation scheme selection to a test engineer at any stage of product development, production and test (both at the factory and in the field). This is another result of our current research in the area of interconnect testing.

A novel Boundary Scan-like Built-In Self-Test (BIST) conception for autonomous at-speed testing and diagnosis of interconnect was developed. It is based on a very efficient design of test pattern generation and response analysis hardware, which allows detection and diagnosis of both static and dynamic faults upon interconnects between chips in a multi-chip environment. The advantages of the new idea were demonstrated over other known methods. It was also shown that the new paradigm brings a never achieved before high level of universality, scalability, and configuration independence into the at-speed interconnect testing and diagnosis of interconnect.

#### <u>New results:</u>

Two new methods for at-speed testing of on-chip buses were proposed.

- 1. The first method is a test application and fault detection scheme that targets the asynchronous nature of NoC links where a Globally Asynchronous Locally Synchronous (GALS) operation principle is utilized. This scheme is the first of its kind available in literature [43].

- 2. The second method represents a flexible programmable embedded test pattern generation solution that supports a tradeoff between test speed and test quality and is designed for multi-layer on-chip bus structures [47].

Both methods primarily target delay faults and harmful interference due to crosstalk, where the second one is an improvement of the Maximum Agressor crosstalk model.

3. A novel Boundary Scan-like Built-In Self-Test (BIST) conception for autonomous atspeed testing and diagnosis of interconnect was developed [28,30,33]. The new paradigm brings a never achieved before high level of universality, scalability, and configuration independence into the at-speed interconnect testing and diagnosis of interconnect.

## 2.7. Fault Simulation Accelerator with Reconfigurable Hardware

Fault simulation is the most often used way of digital analysis and there exist many techniques to speed up simulation<sup>1</sup>. Efficient fault simulation algorithms for combinational circuits are known already for decades. However, it is the large sequential designs whose fault grading run times could be measured in years that drive the need faster implementation, e.g. by hardware emulation. At the same time, reconfigurable hardware, e.g., FPGAs, has been found useful as system-modeling environments<sup>2</sup>. This has been made possible by the availability of multi-million-gate FPGAs. For academic purposes, cheaper devices with rather large capacity, e.g., new Spartan devices, can be used.

The availability of large devices allows implementing not only the circuit under test with fault models but also test vector generator and result analysis circuits on a single reconfigurable

<sup>&</sup>lt;sup>1</sup> P. McGeer, K. McMillan, A. Saldanha, A. Sangiovanni-Vincetelli, P. Scaglia, "Fast Discrete Function Evaluation Using Decision Diagrams." Proc. of ICCAD'95, pp.402-407, Nov. 1995.

<sup>&</sup>lt;sup>2</sup> "Axis Systems Uses World's Largest FPGAs from Xilinx to Deliver Most Efficient Verification System in the Industry." Xilinx Press Release #0273 - http://www.xilinx.com/

device. To study the possibility of replacing fault simulation with emulation, we first had to solve some essential issues - how to represent logic faults in a synthesizable circuit, how to feed the test vectors into the circuit, and how to read and/or analyze the results of emulation? Then we created the experimental environment and performed experiments with some benchmark circuits. The experiments showed that for circuits and/or applications that require large numbers of test vectors, it is beneficial to replace simulation with emulation. More work is needed to integrate the hardware part with the software part of the test generation environment. In addition to merely increasing the speed of fault simulation, the idea proposed in this paper can be used for selecting optimal Built-In Self-Test (BIST) structures.

The emulation environment (Fig. 12) was designed to work together with Turbo Tester (TT) is a diagnostic software package developed at the Department of Computer Engineering of Tallinn University of Technology<sup>3</sup>. The main novelty of the emulation approach lies in implementing MUXes and a decoder for fault injection which, unlike the shift register based injection, allows to insert faults in arbitrary order. This feature is highly useful when applying the presented environment in emulating the test generation process. In addition, we use an on-chip input pattern generator as opposed to loading the simulation stimuli from the host computer. For the first series of experiments, we looked at combinational circuits only. Results of experiments with combinational circuits were presented in [7].

Fig.12. Emulation environment structure

For sequential circuits, most of the solutions used for combinational circuits could be exploited. The main modification was an extra loop in the controller because sequential circuits require not a single input combination but a sequence consisting of tens or even hundreds of input combinations. Also, instead of hard-coded test sequence generators and output analyzers, loadable modules were introduced [76]. To speed up simulation of sequential circuits, an approach with fault dropping was introduced [36]. Before building the experimental environment, we had first to solve how to insert faults, how to generate test vectors, how to analyze output data, and how to automate design flow.

The main problem in fault insertion was how to represent non-logic features - faults - in such a way that they can be synthesized using standard logic synthesis tools. Since most of the analysis is done using stuck-at-one and stuck-at-zero fault models, the solution was obvious use multiplexers at fault points to introduce logic one or zero, or pass through intact logic

<sup>&</sup>lt;sup>3</sup> "Turbo Tester" home page - URL: http://www.pld.ttu.ee/tt/

value. The extra multiplexers will increase gate count and will make the circuit slower (typically 5 to 10 times). For test vector generation and output data analysis, a well-known solution for BIST - Linear Feedback Shift Register (LFSR) - is used both for input vector generation and output correctness analysis<sup>4</sup>. LFSRs structures are thoroughly studied and their implementation in hardware is very simple. This simplifies data exchange with the software part - only seed and feedback polynomial vectors are needed to get a desired behavior. Output correctness analysis hardware needs first to store the expected output signature and then to report to the software part whether the modeled fault was detected or not.

For experiments, a powerful RC1000-PPE board with VirtexE chip (19200 slices) was used. Test circuits were selected from ISCAS'89 and HLSynt'92 benchmark sets to evaluate the speedup when replacing fault simulation with emulation on FPGA. For different benchmarks, the initial hardware emulation was in average 33 (ranging from 13 to 85) times faster than the software fault simulation. The improved environment was in average 250 times faster (from 44 to 517). It should be noted that when considering also synthesis times, it might not be useful to replace simulation with emulation, especially for smaller designs. Nevertheless, taking into account that sequential circuits, as opposed to combinational ones, have much longer test sequences, the use of emulation will pay off. This makes fault emulation very useful to select the best generator/analyzer structures for BIST. Another useful application of fault emulation would be genetic algorithms of test pattern generation where also large numbers of test vectors are analyzed. Future work includes development of more advanced on chip test vector generators and analyzers. [7,36,76]

#### New results:

- 1. A very fast approach to emulate fault simulation of sequential circuits on FPGAs was developed [36,76]. Compared to SW based solutions the speed of fault simulation increased more than 200 times.

- 2. Two alternative approaches were analyzed which can be considered as trade-offs in terms of required FPGA resources and fault grading accuracy. In addition, an environment for reconfigurable hardware emulation of fault simulation was proposed.

- 3. Experiments showed that it is beneficial to use emulation for circuits/methods that require large numbers of test vectors, e.g. simulation-based test pattern generation or validation.

## 2.8. Design for Testability

A comprehensive analysis of different approaches to increase the speed of test generation by improving testability has been carried out. As a result, a new DD based unified approach for calculating mixed-level testability measures was developed and experimented, and a new coarse-grain method was proposed for test point insertion at higher register transfer levels [78].

The method relies on inserting testability components to the RTL VHDL description of the design. The approach is based on non-classical, simplified concept of controllability and observability. The insertion takes place based on the list of uncontrollable and unobservable faults obtained by a sequential ATPG. Such interaction with an ATPG and resynthesis of the device after each test structure insertion would be very time-consuming. The proposed method solves its task with just three iterations. First, a testability analysis is carried out and controllability structures are inserted to the modules containing uncontrollable faults. Then,

<sup>&</sup>lt;sup>4</sup> D.K. Pradhan, C. Liu, K. Chakraborty, "EBIST: A Novel Test Generator with Built in Fault Detection Capability." Proc. of DATE'03, pp. 224-229, March 2003.

the circuit is resynthesized and the ATPG is run. Second, the observability structures are added to the modules, with remaining unobservable faults. Finally, after resynthesis and an ATPG run the overhead area is minimized by removing observability structures from blocks, where there was no increase in fault coverage. A synthesizable VHDL library of dedicated generic components for testability structures has been implemented.

Experimental research with good results was carried out for RTL abstractions. Based on the new testability measures, a new advanced testability guided Register Transfer Level (RTL) Automated Test Pattern Generation (ATPG) for sequential circuits was developed [1,82].

The previous known methods have been implemented in test synthesis and in guiding gatelevel test generation. However, works on application of testability measures to guide highlevel test generation are missing. Experiments showed that testability measures greatly influence the fault coverage in RTL test generation with the proposed approach achieving the best results. The high-level testability measures were used for improving the testability of digital systems by inserting high-level control points [78].

The research on design for testability has been carried out in a close cooperation with Stockholm Royal Institute of Technology in Sweden.

<u>New results:</u>

- 1. A new high-level method for test point insertion for improving the testability of digital systems was developed [78].

- 2. New high-level testability measures were proposed, and using these measures for guiding the ATPG, the speed of test generation was considerably increased [1,82].

## 2.9. Design and Test Research Environment

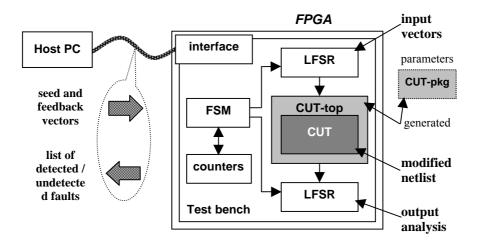

The experimental tools developed in frame of the project formed the basis on which an integrated design and test research environment was created (Fig.13).

Figure 13. Hierarchical design and test research environment

The environment consists of the following parts (groups of tools):

- Synthesis tools (high-level and logic level synthesis)

- Test generation tools (hierarchical, logic and defect level test generators)

- Converters (interfaces between tools)

- Other (university) tools linked to the environment.

Design information can be created in different ways, i.e. by VHDL files to be processed by commercial or experimental high-level or logic synthesis systems, or created manually by schematic editors. The gate-level design is presented in the EDIF format. In university research practice, ISCAS benchmark families which have their own presentation format (ISCAS format) are widely used. In order to link test generation and fault simulation tools with all the needed formats, different converters are developed. EDIF netlists can be converted into ISCAS'85 or ISCAS'89 formats. Necessary technology library files to support such conversion have been created for the research environment.

The Turbo-Tester tools are based on Structurally Synthesized BDDs (SSBDD) they need EDIF-SSBDD to link the tools with commercial CAD systems. Hierarchical ATPG DECIDER uses two inputs – higher level (RTL) descriptions in VHDL and gate-level descriptions in EDIF. For importing VHDL descriptions to DECIDER which uses high-level decision diagrams (DD) as input, a converter VHDL-DD was developed.

As a set of examples, the following design flows can be exercised in this environment.

- 1. An RTL VHDL design is synthesized by high-level synthesis tool. A logic level synthesis for the high-level blocks follows. For these designs DD and SSBDD models are generated. Using DDs and SSBDDs, hierarchical ATPG DECIDER generates test sequences.

- 2. Using SSBDDs, Turbo Tester ATPG generates logic level test patterns targeted to detect logic level stuck-at faults.

- 3. Using SSBDDs and the defect library, the defect-oriented test generator DOT generates test patterns targeted to defect physical defects. The defect libraries available are created in cooperation with Warsaw University of Technology.

- 4. University tools that traditionally use ISCAS benchmarks can be linked via EDIF-ISCAS converter to commercial design tools that produce EDIF format.

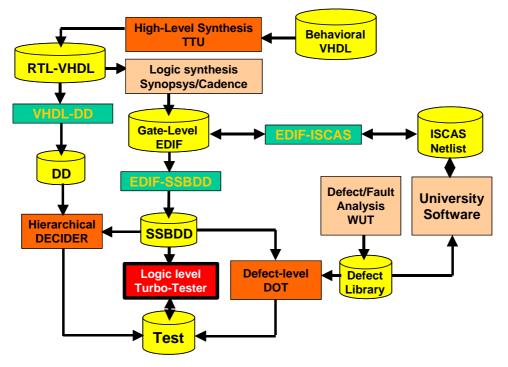

Turbo Tester tool set represents an independent logic level test research environment (Fig.14). The Turbo Tester ATPG software consists of a set of tools for solving different test related tasks by different methods and algorithms:

- Test pattern generation by deterministic, random and genetic algorithms

- Test optimization (test compaction)

- Fault simulation and fault grading for combinational and sequential circuits

- Defect-oriented fault simulation and test generation

• Multi-valued simulation for detecting hazards and analyzing dynamic behaviour of circuits

• Testability analysis and fault diagnosis.

All the Turbo Tester tools operate on the model of Structurally Synthesized Binary Decision Diagrams (SSBDD). The tools of Turbo Tester run on the structural level. Two possibilities are available – gate-level and macro-level. In the latter case, the gate network is transformed into macro network where each macro represents a tree-like sub-network. Using the macro-level helps to reduce the complexity of the model and to improve the performance of tools. The fault model used in the Turbo Tester is the traditional stuck-at one. However, the fault simulator and test generator can be run also in the defect-oriented mode, where defects in the

library components can be taken into account. In this case, additional input information is needed about defects in the form of defect tables for the library components.

Figure 14. Logic level test research environment

The new quality and originality of the environment developed in the project is in the property of multi-functionality of the system (important for research and training), low-cost and ease of use. The multi-functionality means that different abstraction level models can be easily synthesized and resynthesized (to analyze the influence of the complexity of the model to the efficiency of methods), the methods are implemented by different algorithms (to analyze the efficiency of different approaches), the fault models can be easily changed and updated (to analyze the adequacy and accuracy of testing). The multi-functionality allows to set up and modify easily different experimental schemes and scenarios for investigating new ideas and methods.

The multi-functionality gives an excellent opportunity for students working in this environment to understand the ideas, advantages and drawbacks of different methods at changeable conditions. In traditional commercial design tools these purely research oriented possibilities are missing.

Most of the experimental research work carried out in the project was based on this environment. Thanks to this environment an intensive international research cooperation is continuously going on. Subcontractors of the project Fraunhofer Institute in Germany, Linköping University in Sweden, and Technical University Ilmenau have been one group of partners taking actively part in the development and in using this environment. Other partners have been: Warsaw University of Technology in Poland, Slovak Academy of Sciences, TU Darmstadt in Germany, Royal University of Technology Stockholm and University of Jönköping in Sweden a.o.

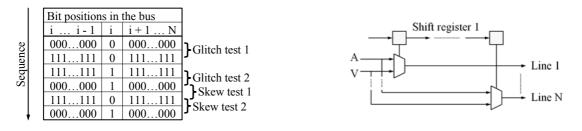

## 2.10. E-Learning Environment for Web-Based Study of Testing

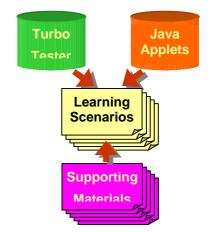

The main goal of the conducted work was the creation of a homogeneous e-learning environment for studying the test and diagnostics of digital systems. In the end, the environment should consist of several interrelated and completed modules shown in Figure 3.

Some of the mentioned modules were partially available; some became implemented during this reporting period, while some others are still to be created or further improved.

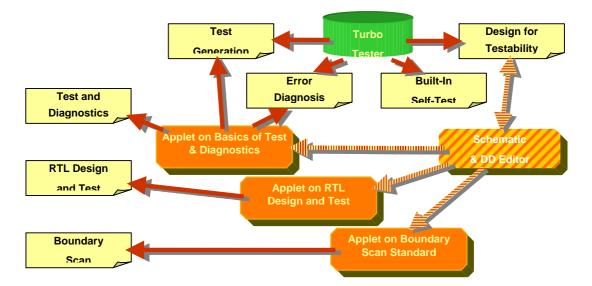

#### The Turbo Tester

The engine [101] of the whole concept consists of PC-based tools installed locally and Java applets invoked remotely via Internet. The PC-based tool set was developed at TTU and it is called the Turbo Tester (TT) [14]. We selected TT for our environment because its range of compatible diagnostic tools forms, via their interaction and complementary operation, a homogeneous research environment, which provides good possibilities for laboratory training and experimental research.

#### The Java applets

The general idea behind the Java applets is a bit different. They are mainly aimed at supporting the concept of game-like style of learning via easy action and reaction, learning by doing, and concentration on most important topics in the simplest possible way. There are three different applets being by now almost ready and having their beta-testing stage running<sup>1</sup>. During the reporting period two of them were updated with new examples and functionality. The fourth applet, which represents a simple schematic and decision

Fig. 15. Overview of the e-learning environment

diagram (DD) editor, was started and it is currently under development. We tried to design our applets in a uniform way; so that the user once got acquainted with the overall style does not have to spend his time learning the new one again from the beginning.

Fig. 16 Relationship between the applets, TT, and research scenarios

<sup>&</sup>lt;sup>1</sup> Java applets home page: http://www.pld.ttu.ee/applets

#### The learning scenarios

The central point of the presented concept is a set of learning scenarios, which describe problems and experiments and represent virtual laboratory works, where students learn diagnostic software and get acquainted with common concepts and problems of testing and diagnostics. There are scenarios for beginners and for advanced study. The user-friendly graphical environment created by the applets is the best option for beginners. More advanced study is possible with scenarios, which make use of TT tools.

#### The general structure

Figure 16 represents an overall structure of relations between the applets, the Turbo Tester, and the learning scenarios. As it is seen from the figure, the advanced scenarios make use of both the TT and the applets. We call them laboratory works<sup>2</sup> since they are usually run in a class equipped with computers having Turbo Tester tools preinstalled. These scenarios were developed in the frames of previous projects and they got incorporated into this new environment. Another group of scenarios, called exercises, were developed during the reporting period. They are better adapted to self-study since together with the corresponding applets they represent platform-independent self-contained systems aimed at teaching target area of knowledge and engineering. Each of the two groups of scenarios should normally be used independently of each other, since there is some overlapping of studied topics.

Another important part of the environment embraces all kinds of supporting materials like user's manuals, help, theoretical reference material, etc. It was substantially updated during the reporting period. In the following, a short description of the applet-based scenarios is given. At the same time, this description covers also the functionality of the related applets. The full text of the scenarios is available in the Web<sup>3</sup>.

#### Basics of logic level testing and diagnostics

This work introduces the very basics of logic-level digital test and diagnosis. Students start with fault sensitization and propagation and justification of signals. First, they learn how to generate a test vector for a particular fault. Then, they continue test generation for all the faults in a given simple circuit. When the test is ready, the task it to minimize the number of test vectors keeping the fault coverage on the same level. Students learn to compare the quality of different test sets. A pseudo-random test sequence is used as a reference here. During test generation, students understand the process of fault simulation and the conception of fault table. They learn to find and distinguish easy and hard-to-test faults. The fault diagnosis considered in the work is of two different kinds. The first one is the sequential diagnosis based on fault table.

#### RTL design and test

Register Transfer level of digital system representation brings a lot of different conceptions to be taught to modern students. We are trying to cover some important topics of RT level design and test in our learning scenario. As in a real electronics system production cycle, the specification of the system comes first. In the current scenario, a certain algorithm, which has to be implemented by a student, plays the role of the specification. The student has to implement different versions of the same algorithm. Each version should meet some specific

<sup>3</sup> <u>http://www.pld.ttu.ee/applets/td/td\_exercises.html</u>

http://www.pld.ttu.ee/applets/rtl/rtl\_exercises.html http://www.pld.ttu.ee/applets/bs/bs\_exercises.html

<sup>&</sup>lt;sup>2</sup> Laboratory training URL: http://www.pld.ttu.ee/testing/labs

design requirement, like low hardware cost or high speed of operation. Students should select a proper structure of the datapath and write a microprogram, which represents the controller. The design validation and verification come next. This is done via simulation at different input data. At the same time, the speed of device operation can be measured. The hardware cost is primarily defined by used datapath resources. The testing for manufacturing defects is the next step of the product life cycle. We use different techniques of test generation (TG) and compare them in our scenario. Since the logic-level TG is considered in previous scenario, we do not pay much attention on it. However, we still give students possibility for revising their high-level test generation attempts on the logic level and for generation of additional test vectors if needed. Among the high-level test methods we single out such generic approaches as Functional Test and Functional BIST (F-BIST). Both methods are based on selection of proper operands in order to get good fault coverage. At this time, the device is working in its normal mode and simultaneously tests itself. The F-BIST technique allows insertion of additional control points for better testability. There are also another two BIST modes: Logic BIST, which is similar to BILBO and Circular BIST, which is analogous to CSTP.

#### Boundary scan standard

The BS standard is a very important state-of-the-art testing technique of modern complex integrated systems. The main goal of the work is to introduce the concept of Boundary Scan to students. They should learn the BS instructions and working modes and see from inside how the BS structures are operating. According to the standard, all the chips on the board are connected into a scan chain via TDI (Test Data In) and TDO (Test Data Out) pins. Hence, all the instructions and test data can be inserted via the single TDI input only. Therefore, the task of controlling the system of several BS chips is not a trivial one. First of all, students should study the Test Access Port (TAP) Controller, which is the key device in the whole BS conception. They learn to move from state to state on the state diagram and insert different BS instructions via TDI. The next step is the study of data registers and their proper usage. When the main principles of BS operation are understood, the students face the task of interconnect diagnosis. They should learn how to properly select test vectors in order to find interconnect defects of a given type. The final and the most advanced task is to write a description of an own chip according to given parameters using BSDL format.

The conception presented here is suitable for a broad audience of learners who are interested in studying different concepts of testing and diagnostics of integrated digital circuits.

## **3. COOPERATION WITH INDUSTRY**

#### 3.1. Cooperation with local industry

In Estonia the group has cooperational links to the following industrial companies: Artec Design, Elcoteq Network Corp., Analog Design AS, Liewenthal, Elvior, M&T Electronics, Cybernetica AS, Borthwick Pignon, AS MicroLink, National Semiconductor Estonia, Testset, Testonica Lab. For these companies our group has regularly organized tutorials or seminars either by the prominent experts from Western countries (Finland, Germany, UK, France etc.) and by the experts of our group.

A close cooperation between TTU and Estonian SME Artec Design (the subcontractor of TTU in WP4) has continued during the last three years. In the framework of this co-operation TTU has transferred its know-how on digital test to the design process of the company [69]. The company has been participated in developing the course materials for TTU.

A new built-in self-test concept has been developed and experimented in System-on-Chip design [48,59]. The new tools developed include software for emulating built-in self-test architectures [20,22,35,95] and tools for hierarchical fault simulation and test pattern generation [54,55].

During the project we had a placement of the group member Jaan Raik in Artec Design.

As a result of the project eVikings II, the Competence Centre of Mission Critical Embedded Systems (ELIKO) has been created (with contracts between 7 private companies and 2 research institutions under the leadership of TTU). Research group runs currently two joint projects with the company Artec Design.

As a result of the project also a new company Testonica Lab was recently created based on the know-how developed in this project.

A close research in the field of Binary Decision Dieagrams is carried out between matematicians of University Tartu and engineers of Technical University Tallinn. A definition of a new class of structurally synthesized BDDs was developed and several new properties of SSBDDs were defined [61,67]. These properies allowed to optimize SSBDDs and to reach higher speed in fault simulation.

#### 3.2. Cooperation with industry outside Estonia

Outside Estonia the group has cooperational links to the following industrial companies: Ericsson AB, SAAB, and DIGSIM DATA AB in Sweden, JTAG Technologies and National Instruments in Sweden, Fraunhofer Institute of Integrated Circuits in Germany, and Insight Memex/Xilinx in France.

Industrial companies Ericsson AB and SAAB in Sweden are strongly interested in the competence of our group and in using it for developing new tools for supporting new

Boundary Scan standards, which are still under the development. This interest is based on our demonstration of the tools we have developed for modeling Boundary Scan processes at different conferences [28,30,33,34,53,85,87,]. Two presentations on these tools have been assigned the **Best Paper Award** [34,87].

Currently, the negotiations to set up a contract between TTU, Testonica Lab, Ericsson and SAAB are going on.

A tight cooperation has taken place between our group and the Fraunhofer Institute of Integrated Circuits in Dresden (Germany), which has been devoted to building up an internet based collaborative design and test environment.

In this cooperation the ATPG tool DECIDER developed at TTU has been adapted to the design flow used in the industry, and excellent results have been achieved in using the ATPG for several industrial designs. For example, it has been shown that the functional test for Huffmann decoder used in the industry had very low fault coverage (less than 20%). The fault coverage for this module was considerably improved by using DECIDER (up to 60%). Suggestions were developed for improving the testability of the module to reach further increase in the fault coverage.

A novel environment for an Internet-based co-operation in the field of design and test of digital systems has been developed in cooperation with Fraunhofer Institute (Germany). The test tools developed by our group can be run at geographically different places under the virtual environment MOSCITO developed in Germany.

As the result of this cooperation, 2 joint papers were published [62, 91].

In cooperation with DIGSIM DATA AB (Linköping, Sweden) a tool exchange has taken place. The diagnostic tool set Turbo Tester developed at TTU was used for teaching industrial engineers in Sweden on one hand, and the design environment DIXIcad developed in the company is being used in the educational environment at TTU for carrying out laboratory works for more than 100 students per year. DIGSIM DATA AB has also carried out a tutorial for students and engineers in Estonia.

JTAG Technologies and National Instruments in Finland have carried out twice a course on Boundary Scan Technology. One of our lab members Dr. Artur Jutman participated in these courses as a lecturer. JTAG Technologies was interested in the Boundary Scan applet developed by our group and expressed the wish to use this applet in their courses. Some extensions are being developed in this applet according to suggestions of JTAG Technologies.

## 4. ACADEMIC INTERNATIONAL COOPERATION

WP4 has cooperated with more than 20 academic institutions from 11 countries (USA, Germany, Sweden, Denmark, Czech Republic, Slovakia, Poland, Bulgaria, Russia, Ukraina and Byelorussia).

Especially intensive was collaboration with subcontractors: Fraunhofer Institute of Integrated Circuits in Dresden, TU Ilmenau (Germany) and Linköping University (Sweden) which resulted in 28 joint publications. In total, 50 joint papers were written with 35 researchers from 18 academic institutions of 11 countries (the total number of paers published in WP3 was 105).

#### 4.1. TU Ilmenau, Germany (Subcontractor S16)

Cooperative work with Technical University of Ilmenau (Germany) had the goal to develop new conceptions, methods and tools for internet based higher education in the field of design and test. The results are published in joint papers [34, 41, 42, 51, 53, 57, 66, 74, 75, 81, 89, 100, 103]. Further joint publications are currently being prepared.

The following students were sent to TU Ilmenau for a placement for 1-3 months: A.Jutman, S.Devadze, V.Rosin, R.Gorjachov, A.Chernov, J.Smahtina, N.Mazurova and A.Sergejev.

The results of the placements of our students at TU Ilmenau are as follows:

- Register Transfer Level Design and Test applet was developed, and the library of components was created (responsible for this work were S.Devadze, N.Mazurova, J.Smahtina). The address of the web site is: <a href="http://www.pld.ttu.ee/applets/rtl/">http://www.pld.ttu.ee/applets/rtl/</a>.

- The Boundary scan applet was developed and equipped with a lot of working modes (responsible for this work were A.Jutman and V. Rosin). The address of the web site is: <u>http://www.pld.ttu.ee/applets/bs/</u>.

- An educational web site was developed where a lot of applets, exercises, laboratory works and corresponding theory on digital design and test has got reviewed, updated and reorganized (responsible for this work were A.Jutman and V. Rosin). The address of the web site is: <u>http://www.pld.ttu.ee/applets/index.html#testing</u>

The educational environment developed jointly support university courses on digital electronics, computer hardware, testing and design for testability to learn by hands-on exercises how to generate test patterns, and how to analyze their quality. The tasks chosen for hands-on training represent simultaneously real research problems, which allow to foster in students critical thinking, problem solving skills and creativity

In this cooperation other institutions took also part resulting in joint publications:

- Institute of Integrated Circuits of Slovak Academy of Sciences, Slovakia

- TU Sofia, Bulgaria

- Warsaw University of Technology, Poland

- Vladimir State Technical University, Russia

- Lviv Polytecnic National University, Ukraine

- Belorussian State University of Informatics and Radioelectronics

- Belorussian State University

#### 4.2. Fraunhofer Institute of Integrated Circuits (Subcontractor S15)

A novel environment for an Internet-based co-operation in the field of design and test of digital systems was jointly developed. The test tools created by our group can be run at geographically different places under the virtual environment MOSCITO developed in Germany.

The following students had the placement in this institution: E.Ivask, J,Raik, A.Jutman.

As the result of this cooperation, 2 joint papers were published [62, 91].

#### 4.3. Linköping University, Sweden (Subcontractor S14)

The topic of cooperation is research and development of new architectures of hybrid BIST for digital systems, formulating and solving optimizational tasks for test processes under the criteria like minimization of test time, peak power and energy consumption, memory requirements and and area overhead and improving the test quality and fault coverage.

Joint research with Linköping University has resulted in a series of papers on the emerging field of built-in self-test of SoC [5, 21, 22, 26, 35, 50, 52, 60, 77, 95-97], and further joint publications are currently being prepared.

#### 4.4. Tomsk State University

The topic of cooperation is joint research on the model of Binary Decision Diagrams (BDD), and especially investigation of the properties of Structurally Synthesized BDD-s with the goal to use these properties for improving the efficiency of logic level test generation algorithms. Two joint papers were published [3,4].

#### 4.5. Donetsk State University

The topic of cooperation is investigation of evolutionary approaches to test generation for functional BIST is considered. Several methods of deriving deterministic test sets at functional level were investigated, and one of them was implemented. Experimental data showed the efficiency of the proposed method [29,70].

#### 4.6. Jönköping University

The joint research topic is interconnect testing in System-on-Chips and Networks-on-Chips with special interest of crosstalk errors. Testing of chips built using deep sub-micron technology is becoming harder since crosstalk and small variations in the fabrication processes are adversely affecting circuit dynamic behaviour. We have developed a conservative method that has the property that it can detect all faulty chips but may also label some good chips as faulty with a small probability [43]. It is possible to extend our method to combine it with functional testing of the link and adapt it for on-line testing. Another method and the corresponding BIST hardware were developed for at-speed testing of crosstalks [47]. The proposed BIST hardware is programmable and can provide the trade-off between test speed and test quality.

#### 4.7. Kharkow National University of Radioelectronics

The main cooperation activity with KNURE is joint organization of the annual IEEE East-West Design & Test Workshops to bring together scientists from East and West. The workshop has taken place already 3 times in 2003-2005. They have been successful events and attracted more then 60-70 participants annually. The first workshop organized in the frame of this project in

September 2003 had a great success and got high interest from IEEE Computer Society and the Test Technology Technical Committee (TTTC) [8]. Now the conference has the IEEE label [11].

#### 4.8. Stockholm Royal University of Technology, Sweden

The cooperation topics are different aspects of developing methods for designing digital systems. In design for testability field a new method for high-level testability measuring were developed [78]. A co-author V.Govind from KTH defended at TTU his MSc thesis, and he will continue in Tallinn also his PhD study. A cooperation is carried out also in the field of design of asynchronous circuits [49].

#### 4.9. Defect-oriented testing

In this topic the cooperation has taken place between:

- TU Darmstadt, Germany